FinFET processes provide power, performance, and area benefits over planar technologies. Yet, a vexing problem aggravated by FinFET’s is the greater local device current density, which translates to an increased concern for signal and power rail metal electromigration reliability failures. There is a critical secondary effect, as well – the thermal profile of the FinFET influences the temperature of the metal interconnect neighborhood, which accelerates the EM failure rate probability.

At the recent TSMC OIP symposium, Ansys/Apache provided exceptional insights into the issue, and how their toolset assists designers with EM analysis at advanced nodes.

The “Self-heating effect”

Self-heating refers to the thermal energy originating at a current-carrying element. The local temperature rise depends upon the thermal dissipation path(s) away from the element. The model for thermal conduction uses an electrical equivalent – heat flows through a “thermal resistance”, which is characteristic of the materials surrounding the source.

FinFET self-heating has unique thermal resistances from the device channel. Unlike planar (non-SOI) devices, the thermal path through the substrate is constrained by the poor thermal conductivity of the dielectric at the base of the fin. As a result, a significant percentage of the device self-heat energy flows vertically and laterally to the MEOL metallization, with a delta_T increase in the metals.

Note: FinFET self-heat dissipation also has an adverse impact on instrinsic device reliability mechanisms, such as bias temperature instability (BTI) and hot carrier injection (HCI). A subsequent article will review TSMC OIP presentations on FinFET “device aging” models and self-heat acceleration.

In addition to heat transfer from FinFET devices, there is a temperature increase in interconnects due to wire self-heating – namely, the resistive losses in the metal. There is also heat transfer from the resistive dissipation in neighboring interconnects.

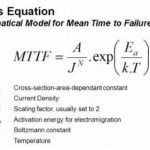

The EM induced failure rates – i.e., the “mean time to fail” probability – due to the average current density in a metal wire is typically represented by Black’s equation:

(For more background on EM, please see the semiwiki article:

https://www.semiwiki.com/forum/content/1085-ic-custom-ip-blocks-electromigration-em-ir-drop-effects.html )

Note the exponential dependence on temperature in this model. The delta_T in a wire above the local die temperature due to heat transfer and resistive self-heating requires a sophisticated thermal resistance model and power dissipation analysis, which Ansys has developed and qualified with TSMC.

Ansys flow for enhanced EM analysis

Ansys is an industry leader in electromigration analysis (RedHawk, Totem), and in thermal modeling and analysis of the chip-package-system environment (RedHawk, Sentinel-TI, Icepak). The on-chip extraction features of this toolset have been enhanced to support multi-patterning decomposition “color aware” metal biasing of TSMC’s advanced FinFET nodes. To address the requirements for delta_T in electromigration analysis, new tool capabilities have been added, and a new flow qualified.

The key new feature is the characterization of the interconnect temperature to include the thermal sources mentioned earlier. Starting with the (tile-based) Chip Thermal Model without self-heat, a new solution for the interconnect temperature with device and wire self-heat contributions is derived using the chip-package thermal analysis tools.

There are a number of different methods used to determine an electromigration-based chip reliability estimate. The most direct approach is:

- assume a max allowable increase in interconnect (or via) resistance over a product lifetime due to EM (e.g., x%)

- measure the average current density on test wafers which results in that delta_R – this is an accelerated stress test applied to various interconnect structures

- using Black’s equation, adjust the measured J_average current density limit from the stress test to the product environment

For example, when deriving the J_average limit, assume the MEOL wire temperature is equal to Tj_max plus a small delta_T due to the wire’s intrinsic J_rms self-heating – e.g., 105 degrees C. + 5 degrees delta. The J_average limit may actually be a set of tables using the interconnect width and length. Electromigration current density limits are a function of the metallurgy of the materials – e.g., metal grain size versus width – and are greatly reduced for short length segments (below the “Blech length”).

- calculate the thermal resistances between devices and wires for the delta_T characterization

- using the Ansys flow, calculate the detailed wire temperatures

- if the wire J_average and temperature are below the process reliability limits, assume the interconnects do not contribute significantly to the reliability MTTF; else, highlight these as electromigration “hot spots” which need addressing

Ansys has enhanced their tools and flows to address a key reliability issue in FinFET technologies – the potential for significant delta_T on interconnects/vias due to thermal coupling, and the resulting acceleration of electromigration reliability failures.

This is a good example of the benefits of the “early” EDA vendor partnership with TSMC that Cliff Hou highlighted during his OIP keynote presentation.

-chipguy

Also read: Four Takeaways from the TSMC OIP 2015