-ASML reports better results & guide despite China restrictions

-Supports our view of China issues not that impactful longer term

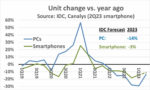

-Industry recovery seems very far off with more delays

-ASML remains the best, most robust story in a weak industry

ASML reports nice beat despite China concerns

ASML reported revenues of Euro6.9B of which Euro5.6B was for systems with EPS of Euro4.93 . This is roughly $7.52B in revenues and $5.37 in EPS versus street estimates of $7.48B and $5.10…so a nice beat.

Guidance is for between Euro6.5B and 7.0B in revenues. At the midpoint this is roughly $7.57B versus expectations of $7.14B.

Margins remained above 50%.

Perhaps most importantly, ASML expects that growth in 2023 will be roughly 30% above that of 2022 which is up from prior expectations of 25-27%.

All in all a very good quarter despite industry weak conditions and macroeconomic uncertainty.

Confirms our view that China impact is minimal and not significant

We have suggested since the start of sanctions on the sale of litho tools to China that the overwhelming demand for ASML’s tools would more than offset tools impacted by sanctions. This appears to be the case as demand from China for older technology tools is stronger than ever.

We think investor concerns continue to be overblown as overall demand remains quite strong despite the prolonged industry downturn.

Semiconductors remains a zero sum game

In the long term, semiconductor production will remain a zero sum game. By that we mean that chips not produced in China will have to be produced elsewhere by some other country perhaps at a slightly higher cost but using the same ASML tools that China would have otherwise bought.

In a way, the restrictions on sales to China may help to diversify demand and chip production across the globe so that China does not dominate both the purchase of tools as well as production.

While this may cause disruption in the near term it likely is better for all in the long term as it prevents the total domination we have seen from China in both the solar and LED markets. We wouldn’t want what happened in those markets to happen in the much more critical chip market.

We strongly maintain our belief in the control of exports of chip equipment to China to prevent that from happening for both defense and economic concerns.

China is buying plenty of DUV tools anyway

Its certainly not like China isn’t buying a lot of tools from ASML as they can still buy DUV tools and continue to do so in large quantity. The DUV business for ASML remains quite robust at almost 50% of overall business. Up from prior quarters.

Memory even worse than before, almost down by 50% Q/Q

While logic and foundry, especially in trailing edge remains strong, memory continues its nosedive with memory related sales dropping by almost half quarter over quarter from 30% of sales in Q1 to just 16% of sales in the just reported quarter.

As we have continued to repeat…memory is very, very ugly. There is no recovery in sight and capex continues to trend down in memory to just sustenance levels and no more

Fab delays are impactful

We had mentioned in our note from SEMICON West last week that we were growing concerned about delays in planned fab construction and likely further delays and cancelations as capacity is clearly not needed in foundry/logic and especially not in memory which is swimming in capacity.

ASML pointed out that fab utilization remains low which means tool utilization is low. ASML said that fab delays are delaying and pushing out deliveries of equipment.

We clearly haven’t seen the end of this and fab delays will likely worsen as the downturn extends into next year.

Right now we are just seeing delays but some of that could turn to cancelations if the fabs they were intended for get canceled.

Fantastic job on DUV offsets weakness to some extent

ASML is now talking about shipping a staggering 375 DUV tools of which 25% would be immersion. Rather than Euro3B of revenue that was expected to be delayed from 2023 to 2024, ASML has instituted some fast ship protocols and will see an additional Euro700M in 2023.

This helps offset other weakness and contributed to increasing the overall 2023 growth rate.

This obviously helps make up for slowing EUV sales which were expected to grow 40% Y/Y but now expected to grow only 25% Y/Y.

The book to bill wasn’t great with Euro4.5B in orders but the backlog remains strong and long at Euro38B, a huge number that will continue to keep ASML warm through the now lengthened chip winter.

Somewhat worse news on industry downturn confirms our pessimistic view

We have been suggesting since the beginning of this downcycle almost a year ago that this down cycle would be worse than most due to a variety of circumstances. This appears to be the case and the prolonged downturn seems to have been communicated in ASMLs report as they had essentially no hint of a recovery and a number of factors worsened.

We have also clearly communicated that we can’t have a significant recovery of the overall industry without memory recovering as well….it just doesn’t happen that way.

Right now memory is as bad as ever. Pricing remains low, bloated inventories, lowered production, cut capex…..all bad signs on top of macro economic issues.

AI is not the savior of AI and we think investors may be figuring that out

The stock- A beautiful mansion with a moat in an ugly neighborhood

If we had to buy one semiconductor equipment stock ASML would be it. Growing 30% Y/Y during a downturn is just amazing. They are a true monopoly with dominant market share and technology with zero competition.

China issues are not impactful in our view and could offer long term benefit.

The long term semiconductor view remains very positive.

The obvious problem is that in the near term the industry remains ugly. ASML will outperform the group by far during the downturn as they are already proving. They will also be the first out of the downturn as litho tools are the first thing you buy for your new fab.

We would equate ASML to being a beautiful, well built mansion with a deep moat around it in a neighborhood that is going through a difficult period of transition.

It may be the best home in town but investors may be concerned about buying in at this particular point in time given the overall neighborhood condition, thus we will see a weak stock despite financial & technical out performance.

We view this report more negatively for others in the semiconductor equipment space as it suggests a longer downturn that we have predicted and as we mentioned last week, investors may start to get impatient as the recovery seems further away tahn hoped.

Also Read:

SEMICON West 2023 Summary – No recovery in sight – Next Year?

Micron Mandarin Memory Machinations- CHIPS Act semiconductor equipment hypocrisy

AMAT- Trailing Edge & China Almost Offset Floundering Foundry & Missing Memory