The first AI Generated Open-Source Silicon Design Challenge invited participants to use generative AI to design an open-source silicon chip and tape it out in just three weeks. The contestants were required to create Verilog code from natural language prompts, and then implemented their designs using the chipIgnite platform and the OpenLane open-source design flow.

The challenge was a success, with participants from all over the world, some of whom had never designed a chip before, and virtually none of whom had previously used OpenLane. Six designs successfully met all the criteria, and in a very close call, three designs were declared to be the winners by our outside panel of judges based on pre-determined criteria including design completeness, documentation, technical merit, and community interest.

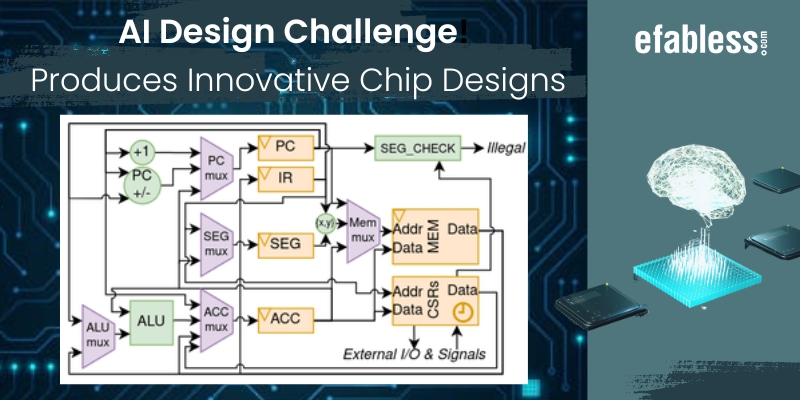

The first-place winner of the contest was QTCore-C1 by Hammond Pearce at New York University. The design is a co-processor that can be used for many applications, such as predictable-time I/O state machines for PIO functions as seen on some microcontrollers developed using the Chip-Chat methodology that the NYU team has published.

The second-place winner of the contest was Cyberrio by Xinze Wang, Guohua Yin, and Yifei Zhu at Tsinghua-Berkeley Shenzhen Institute. This design is a RISC-V CPU, implemented with Verilog code produced via a series of prompts given to ChatGPT-4.

The third-place winner of the contest was Asma Mohsin at Rapid Silicon. The design is a Model Predictive Control (MPC) that is used to predict future behavior and optimize control actions for a regulator control circuit provided in MATLAB code to ChatGPT-4 and then implemented with prompts in Verilog.

The designs were all very impressive, and all the participants successfully demonstrated how tools such as ChatGPT, Bard and others can revolutionize chip design by automating many of the tedious tasks involved in the development process, making it simpler, faster and more efficient.

Efabless will now fabricate the three winning designs on its chipIgnite shuttle. The winners will receive packaged parts and evaluation boards, valued at $9,750 each. In addition, all participants with qualifying designs will receive a free evaluation board and one of the winning AI-generated chips.

Efabless will shortly be featuring videos from the various winning designs and teams describing their experience and lessons learned.

Efabless will also soon release information about the second AI-Generated Design Challenge. The challenge will take place over the summer, with tapeouts expected in September. Stay tuned!

About Efabless

Efabless offers a platform applying open source and community models to enable a global community of chip experts and non-experts to collaboratively design, share, prototype and commercialize special purpose chips. Nearly 1,000 designs and 450 tapeouts have been executed on Efabless over the past two years. The company’s customers include startups, universities, and research institutions around the world.

Also Read:

Why Generative AI for Chip Design is a Game Changer

Join the AI Generated Open-Source Silicon Design Challenge!

A User View of Efabless Platform: Interview with Matt Venn

Share this post via:

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!