You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Improved profitability and competitiveness are at the very heart of every enterprise. Achievements like this are usually attributed to corporate culture. Sometimes, it’s just being in the right place at the right time. Some organizations make huge investments with top-tier consulting companies to help find their way.

Recently… Read More

Whether it is the stock market or the semiconductor market, the name of the game is yield. In semiconductors, yield has to do with minimizing scrap costs in all phases of manufacturing. This means squeezing as many good dies from a wafer as well as maximizing the number of good assembled/packaged chips that pass system level testing.… Read More

There is an old saying popularized by Mark Twain that goes “There are three kinds of lies: lies, damned lies, and statistics.” It turns out that no one can say who originated this saying, yet despite however you might feel about statistics, they play an important role in verifying analog designs. The truth is that there are large numbers… Read More

The letters “PVT” roll of the tongue easily enough, belying the complexity that variations in process, temperature and voltage can cause for analog designs. For semiconductor processes, there are dozens of parameters that can affect the viability of a design. It would be easy enough to optimize a circuit with only one or two varying… Read More

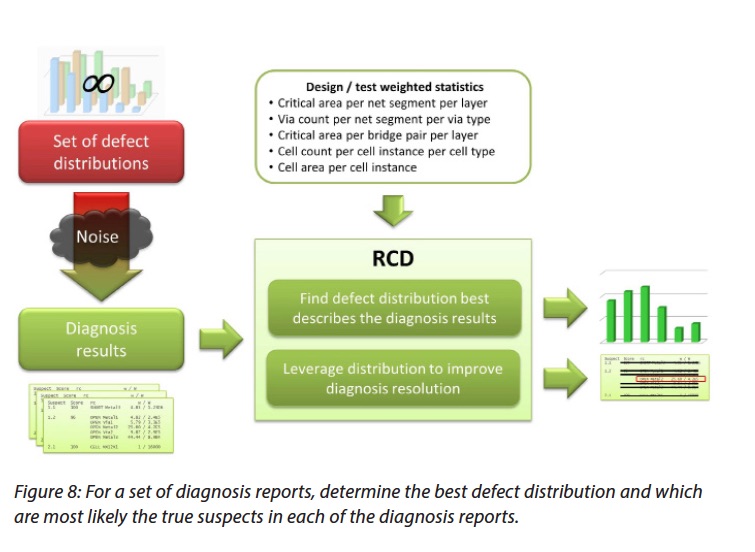

Naturally, chips that fail test are a curse, however with the advent of Scan Logic Diagnosis these failures can become a blessing in disguise. Through this technique information gleaned from multiple tester runs can help pin down the locations of defects. Initially tools that did Scan Logic Diagnosis relied on the netlist to filter… Read More

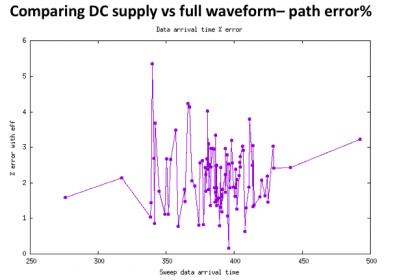

About 6 months ago, ANSYS was approached by a couple of leading mobile platform vendors/suppliers with a challenging problem. These companies were hitting target 2.5GHz performance goals on their (N10 or N7) application processors, but getting about 10% lower yield than expected, which they attributed to performance failures.… Read More

Have you notice how smart your automobile is getting? Watching the first round of NFL playoffs I lost count on the number of TV commercials showing cars weaving through tight construction zones (and Star Wars figures), big trucks parking in incredibly tight spaces, cars avoiding rear-end collisions and pedestrians, and even … Read More

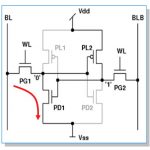

My IC design career started out with DRAM at Intel, and included SRAM embedded in GPUs, so I recall some common questions that face memory IP designers even today, like:

- Does reading a bit flip the stored data?

- Can I write both 0 and 1 into every cell?

- Will read access times be met?

- While lowering the supply voltage does the cell data retain?

…

Read More

In a power hungry world of semiconductor devices, multiple ways are being devised to budget power from system to transistor level. The success of IoT (Internet of Things) Edge devices specifically depend on lowest power, lowest area, optimal performance, and lowest cost. These devices need to be highly energy efficient for sustained… Read More

It gives me a very nice, somewhat nostalgic, feeling after attending the 52[SUP]nd[/SUP] DAC. There was a period during my final academic year in 1990 and my first job when I used to search through good technical papers in DAC proceedings and try implementing those concepts in my project work. In general, representation from ‘R&D… Read More