When I was at Atrenta, we always thought it would be great to do as-you-type RTL linting. It’s the natural use model for anyone used to writing text in virtually any modern application (especially on the Web, thanks to Google spell and grammar-checks). You may argue that you create your RTL in Vi or EMACS and you don’t need no stinking… Read More

Tag: verilog

High Level Synthesis Update

High-level synthesis (HLS) involves the generation of an RTL hardware model from a C/C++/SystemC description. The C code is typically referred to as abehavioraloralgorithmicmodel. The C language constructs and semantics available to architects enable efficient and concise coding – the code itself is smaller, easier to write/read,… Read More

Leveraging HLS/HLV Flow for ASIC Design Productivity

Imagine how semiconductor design sizes leapt higher with automation in digital design, which started from standard hardware languages like Verilog and VHDL; analog design automation is still catching up. However, it was not without a significant effort put in moving designers from entering schematics to writing RTL, which… Read More

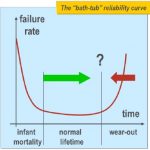

Predicting Lifetime of Analog ICs

With the increase of transistors per unit area, high density interconnects and manufacturing variability at lower nodes, the electronic devices have become more vulnerable to failures. The devices that operate under extreme conditions such as automotive devices that operate at high temperatures need to be robust enough to… Read More

Successful Venture of an Indian Global VIP Company

It’s rare that we find a truly Indian-based company operating globally in the semiconductor space. Although the ‘gold rush’ towards IP development in the last decade initiated many IP start-ups in India, today we rarely find Indian IP company names which are shining in the global arena. The story of services companies is different,… Read More

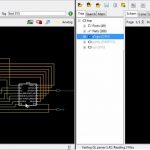

Starvision Pro: Lattice Semiconductor’s Experience

During SNUG I took the opportunity to chat to Choon-Hoe Yeoh of Lattice Semiconductor about how they use Concept Engineering’s Starvision Pro product. He is the senior director of EDA tools and methodologies there.

Lattice Semiconductor is a manufacturer of low-power, small-footprint, low-cost programmable logic devices.… Read More

A Comprehensive Automated Assertion Based Verification

Using an assertion is a sure shot method to detect an error at its source, which may be buried deep within a design. It does not depend on a test bench or checker, and can fire automatically as soon as a violation occurs. However, writing assertions manually is very difficult and time consuming. To do so require deep design and coding… Read More

Expert Tool to Easily Debug RTL and Reuse in SoCs

SoC design these days has become a complex and tricky phenomenon involving integration of multiple IPs and legacy RTL code which could be in different languages, sourced from various third parties across the globe. Understanding and reusing RTL code is imperative in SoC integration which needs capable tools that can accommodate… Read More

StarVision to Debug and Analyze Designs at All Levels

In today’s SoC world where multiple analog and digital blocks along with IPs at different levels of abstractions are placed together on a single chip, debugging at all levels becomes quite difficult and clumsy. While one is working at the top level and needs to investigate a particular connection at an intermediate hierarchical… Read More

Design & EDA Collaboration Advances Mixed-Signal Verification through VCS AMS

Last week it was a rare opportunity for me to attend a webinar where an SoC design house, a leading IP provider and a leading EDA tool provider joined together to present on how the tool capabilities are being used for advanced mixed-signal simulation of large designs, faster with accuracy. It’s always been a struggle to combine design… Read More