Although semiconductor community has ushered into the era of SoCs, the verification of SoCs is still broken. There is no single methodology or engine to verify a complete SoC; this results in duplication of efforts and resources for test creation and verification at multiple stages in the SoC development, albeit with different… Read More

Tag: verification

Aldec extends FPGA and ASIC flows at DAC

Aldec tools and services have long been associated with FPGA designs. As FPGAs have evolved toward more RTL-based designs, the similarities between a modern FPGA verification flow and an ASIC verification flow often leave them looking virtually the same. … Read More

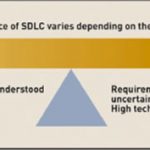

Bringing Formal Verification into Mainstream

Formal verification can provide a large productivity gain in discovering, analyzing, and debugging complex problems buried deep in a design, which may be suspected but not clearly visible or identifiable by other verification methods. However, use of formal verification methods hasn’t been common due to its perceived complexity… Read More

Webinar alert – Taking UVM to the FPGA bank

UVM has become a preferred environment for functional verification. Fundamentally, it is a host based software simulation. Is there a way to capture the benefits of UVM with hardware acceleration on an FPGA-based prototyping system? In an upcoming webinar, Doulos CTO John Aynsley answers this with a resounding yes.… Read More

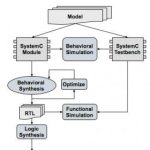

SystemC and Adam’s Law

At DVCon I sat in on a series of talks on using higher-level abstraction for design, then met Adam Sherer to get his perspective on progress in bringing SystemC to the masses (Adam runs simulation-based verification products at Cadence and organized the earlier session). I have to admit I have been a SystemC skeptic (pace Gary Smith)… Read More

Design units come to faster Riviera-PRO release

For the latest incremental improvements to its Riviera-PRO functional verification platform, Aldec has turned to streamlining random constraint performance. The new Riviera-PRO 2016.02 release also is now fully supported on Windows 10 and adds a new debugger tool.… Read More

FPGA tools for more predictive needs in critical

“Find bugs earlier.” Every software developer has heard that mantra. In many ways, SoC and FPGA design has become very similar to software development – but in a few crucial ways, it is very different. Those differences raise a new question we should be asking about uncovering defects: earlier than when?… Read More

HW/SW Interfaces for Portable Stimulus

With growing size and complexity of SoC, the semiconductor community is realizing the growing pain of verification. The cost of SoC verification grows exponentially with design size. Moreover, there is no single methodology for verifying a SoC; multiple engines are used in different contexts through different verification… Read More

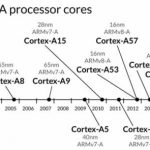

Mentor ARM subscription signals ecosystem shift

Since creating the landmark “all-you-can-eat” license with Samsung in 2002, ARM has inked several subscription deals with chipmakers and EDA firms. The latest ARM subscriber license deal just announced is for Mentor Graphics. What makes their strategy unique?… Read More

Synopsys at DVCon 2016

It’s that time of year again – DVCon starts on Monday Feb 29[SUP]th[/SUP] and as always should be a packed event. Synopsys plans a big showing, in the exhibit hall, in a sponsored lunch, at tutorials and in papers. Time to get your conference shoes on and go check them out – I plan to be there all week.

One of the most obvious things you will… Read More