Semiconductor design automation at system level is gaining its due importance today. It needs an effective, efficient, and seamless flow from system up to silicon. There is lot of effort going on for automating SoC design exploration at system level but that eventually stops at RTL; another level of flow automation takes over … Read More

Tag: synthesis

A New Unified Power Solution at All Levels

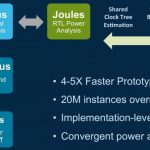

When situation demands, multiple solutions appear with a slight lag of time. Similar is the story with estimating and optimizing power at SoC level. In the SoC era, power has become a critical criterion long ago, and there are tools available for power analysis and optimization. However, with more mobile and IoT (Internet of Things)… Read More

Ultra-low Voltage: Is Your Slack Really Positive? Are You Sure?

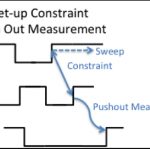

During synthesis and static timing the main figure of merit is “slack”. If a signal arrives with time to spare before it is needed (often measured against the setup time before a clock changes at a register) then the slack is positive. Positive slack is generally a good thing, although it can indicate over-design if … Read More

More FPGA-based prototype myths quashed

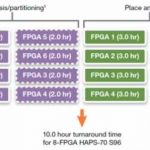

Speaking of having the right tools, FPGA-based prototyping has become as much if not more about the synthesis software than it is about the FPGA hardware. This is a follow-up to my post earlier this month on FPGA-based prototyping, but with a different perspective from another vendor. Instead of thinking about what else can be done… Read More

Synflow and Cx

When hardware designers hear about a new language their heart sinks. We already have Verilog, SystemVerilog and VHDL. And if you go up a level, we have C, C++ and SystemC. Isn’t that enough? However, if you tell a software engineer about a new language they are interested, there are hundreds of programming language and hundreds… Read More

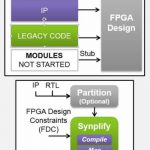

Dealing with FPGA IP in all its forms

One of the recurring themes I see here in the pages of SemiWiki and elsewhere is this pitched, bordering on religious battle between Altera and Xilinx. Just because both are FPGA technologies, the tendency is to put them in the same bucket, drawing direct comparisons between them. Some folks say there is no comparison; Xilinx has… Read More

Concept: From Schematics to Debug

In the late 1990s I was the VP Engineering at Ambit Design Systems. We had a synthesis product (called BuildGates, nobody ever forgot the name). Both our own engineers and our customers wanted to be able to take a look at the gate-level netlist that was generated from their RTL. We used a product from a company called Concept Engineering… Read More

Designing Hardware with C++ and its Advantages

Very recently, I was seeing intense discussions on the need for agile hardware development just like agile software and ideas were being sought from experts as well as individuals. While in software world it has already evolved, in hardware world it’s yet to see the shift in paradigm. My point is that the end goal of agile hardware… Read More

Designing the Right Architecture Using HLS

With the advent of HLS tools, general notion which comes to mind is that okay, there’s an automated tool which can optimize your design description written in C++/SystemC and provide you a perfect RTL. In real life, it’s not so, any design description needs hardware designer’s expertise to adopt right algorithm and architecture… Read More

International Workshop on Logic and Synthesis

There are always a number of other events that are colocated with DAC. One this year is the 23rd International Workshop on Logic and Synthesis (IWLS) that is held the weekend before DAC on May 30th and June 1st. Strictly speaking it is not colocated since it is in the Galleria Park Hotel on Sutter Street a few blocks away whereas DAC itself… Read More