You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Here are the top 10 reasons to use the Xilinx Vivado Design Suite to design your All Programmable Devices:

Reason number 10: Accelerate verification by over 100XThe Vivado Design Suite System Edition lets you do design at the C, C++ or systemC level. But a side-benefit is that you can use these languages for verification at performances… Read More

Mentor is acquiring Oasys, subject to all the usual caveats about shareholder and regulatory approval. The shareholder paperwork went out earlier this week. The common stock is valueless so presumably the price is low (and Mentor historically has not paid high prices for its acquisitions).

So what is going to happen with the technology?… Read More

One area of iteration that is becoming more problematic is between floorplanning and synthesis. So much of timing is driven by placement that fixing timing and even power often involves not just re-synthesis and re-placement but alterations to the floorplan. The Achilles heel of existing methods is that floorplanning tools … Read More

Timing exceptions are ways of guiding design tools, primarily synthesis and static timing analysis (STA), but these days also place & route and perhaps other tools. Most paths in a design go from one register to the next register. Both registers are on the same clock, and the design needs to ensure that the signal can make it from… Read More

There is a new book out from Springer. The subtitle is actually a better description that the title. The subtitle is A Practical Guide to Synopsys Design Constraints (SDC) but the title isConstraining Designs for Synthesis and Timing Analysis. The authors are Sridhar Gangadharan of Atrenta in San Jose and Sanjay Churiwala of Xilinx… Read More

Easy SystemC Debuggingby Randy Smith on 07-03-2013 at 7:00 pmCategories: EDA

Electronic system design has been slowly migrating to higher level languages such as SystemC for more than a decade now. SystemC is an open source C++ library that has emerged as a standard for high-level design and system modeling. Writing code in SystemC has several advantages which I won’t elaborate on in this article, though… Read More

Recently, Forte Design Systems announced the release of a new core engine to their popular high-level synthesis tool offering. It is a large undertaking, so I asked John Sanguinetti, Forte’s CTO, to answer some questions about that development effort.

Q. How long has it been since the last major upgrade of the Cynthesizer… Read More

Today Oasys announced the availability of Floorplan Compiler in the Oasys RealTime suite of physical RTL exploration and synthesis tools. This is actually a repackaging of a capability that has always been in RealTime Designer, and in fact has been an important aspect of how well RealTime Designer has performed in benchmarks … Read More

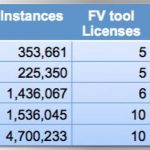

Formal verification can be used for many things, but one is to ensure that synthesis performs correctly and that the behavior of the output netlist is the same as the behavior of the input RTL. But designs are getting very large and formal verification is a complex tool to use, especially if the design is too large for the formal tool… Read More

Oasys Has a New CEOby Paul McLellan on 01-18-2013 at 2:21 pmCategories: EDA

Scott Seaton is the new CEO of Oasys Design Systems. Paul van Besouw, the CEO since the company’s founding, becomes the CTO. I met Scott last year when I was doing some consulting work for Carbon Design where he was VP of sales (the new VP sales at Carbon is Hal Conklin, by the way).

I talked to Scott about why he had joined Oasys. … Read More