Ever sat around waiting for a time slot on the one piece of big, powerful, expensive engineering equipment everyone in the building wants to use? It’s frustrating for engineers, and a project manager’s nightmare: a tool that can deliver big results, and a lot of schedule juggling.… Read More

Tag: synopsys

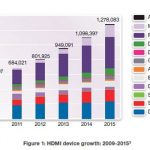

Why integrating HDMI 2.0?

High Definition Multimedia Interface (HDMI) is today part of our day to day life, at home as well as at our office we are using devices integrating HDMI ports. HDMI penetration is well illustrated by this picture (created in Dec. 2011 by In-Stat): from DTV to Game console, the devices belong to the Consumer Electronics market segments,… Read More

Known Unknowns and Unknown Unknowns

Donald Rumsfeld categorized what we knew into known unknowns and unknown unknowns. In a chip design, those unknown unknowns can bite you and leave you with a non-functional design, perhaps even intermittent failures which can be among the hardest problems to debug.

Chips are too big to do any sort of full gate-level simulation,… Read More

Designing a DDR3 System to Meet Timing

My very first thought when hearing about HSPICE is using it for IC simulation at the transistor-level, however it can also be used to simulate a package or PCB interconnect very accurately, like in the PCB layout of a DDR3 system where timing is critical. I attended a webinar this morning that was jointly presented by Zuken and Synopsys… Read More

Conquering errors in the hierarchy of FPGA IP

FPGA design today involves not only millions of gates on the target device, but thousands of source files with RTL and constraints, often generated by multiple designers or third party IP providers. With modules organized in some logical way describing the design, designers brace themselves for synthesis and a possible avalanche… Read More

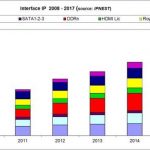

Interface Protocols, USB3, PCI Express, MIPI, DDRn… the winner and losers in 2013

How to best forecast a specific protocol adoption? One option is to look at the various IP sales, it will give you a good idea of the number of SoC or IC offering this feature on the market in the next 12 months. Once again, if you wait for the IP sale to have reached a maximum, it will be too late, so you have to monitor the IP sales dynamic when… Read More

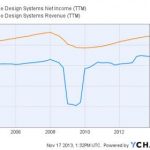

Cadence Design Systems’ Shares Are Surprisingly Cheap

In the third and final (for now) part of this series on the EDA design tool vendors, I’d like to take a closer look at Cadence Design Systems. This is probably the most interesting of the three from both an industry perspective as well as an investment perspective for a variety of reasons. With that said I’d like to first provide some … Read More

Social Media at Synopsys

When I talk about social media and mention Synopsys you may quickly think of Karen Bartleson, the Senior Director of Community Marketing, because she:

- Blogs and podcasts

- Created the best interactive DAC game ever in 2013 using barcodes and points

- Tweets @karenbartleson

- Is president of the IEEE Standards Association

- Has over

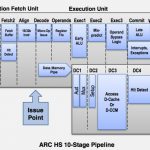

Synopsys Creates a High-performance ARC Core

ARC is a family of configurable processors. Originally it was a standalone company in the UK (what is it with the UK and processor cores?) spun out from Argonaut Software. The A in ARC stood for Argonaut originally. ARC International was acquired by Virage and then Virage was acquired by Synopsys so now it is part of Synopsys Designware… Read More

M-PCIe, Data Converters, and USB 3.0 SSIC at IP SoC 2013

Synopsys is taking IP-SOC 2013 seriously, as the company will hold several presentations, starting with a Keynote: “Virtual Prototyping – A Reality Check”, by Johannes Stahl, Director, Product Marketing, System-Level Solutions, Synopsys, highlighting current industry practice around putting virtual prototyping to work… Read More