At the end of last month during ISSCC there was a forum organized by the SOI Consortium. It took place in San Francisco at the Palace Hotel (which, if you have never been there, is famous for converting its old entryway for carriages into an amazing dining room, and for a bar with a huge painting by Maxfield Parrish of the Pied Piper valued… Read More

Tag: stmicroelectronics

STMicro to Showcase Turnkey NFC Design at MWC

Near-field communication (NFC) technology is finally realizing its potential, thanks to the impetus provided by Apple Pay, and it’s becoming evident from the pre-Mobile World Congress (MWC) buzz coming from several makers of chips, smartphones and wearable devices.

Among the companies displaying NFC products at the 2015 … Read More

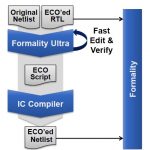

Faster ECOs Using Formal Analysis

Your latest SoC has just begun the tape-out process and then marketing comes back with a small update to the specification to make your design more competitive, or maybe your regression tests just found a minor bug in a single IP block that needs to be fixed. Should you go back in your design flow, change the RTL source code and then completely… Read More

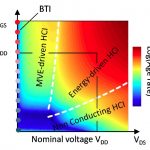

Advantages when Designing with FD-SOI

In total we have blogged 41 times about FD-SOI on SemiWiki which has drawn an audience of 202,960 thus far. Of that traffic 31.68% came directly to SemiWiki (Newsletter), 30.13% came from search, 26.17% from social media (LinkedIn, FaceBook, Twitter, Google+, Reddit, etc…), and 11.99% came from other referring sites. The most… Read More

STMicroelectronics and SoCs

What does system on chip (SoC) actually mean? How this tech moniker came into being? There is quite a bit of enigma about SoC in the technology press and what this term really stands for. Roger Shepherd, consultant at Parallel Computer Systems, shares on Quora his version of the SoC story. He says that he first heard about SoCs when … Read More

Ensuring Safety Distinctive Design & Verification

In today’s world where every device functions intelligently, it automatically becomes active on any kind of stimulus. The problem with such intelligence is that it can function unfavorably on any kind of bad stimulus. As the devices are complex enough in the form of SoCs (which at advanced process nodes are more susceptible to … Read More

IO Design Optimization Flow for Reliability in 28nm

User group meetings are a rich source of information for IC designers because they have actual designers talking about how they used EDA tools in their methodology to achieve a goal. Engineers at STMicroelectronicspresented at a MunEDAUser Group on the topic: I/O Design Optimization Flow For Reliability In Advanced CMOS Nodes.… Read More

Samsung Endorses FD-SOI!

This is probably one of the biggest stories we will cover this month, if not this year, absolutely. In partnership with STMicroelectronics, Samsung will manufacture 28nm FD-SOI chips for the fabless semiconductor community starting now. This proves without a shadow of a doubt that Samsung is serious about the foundry business.… Read More

FD-SOI, FinFET, 3D in Monterey

Last night the IEEE Silicon Valley Chapter had a panel session that was in some ways a preview of some of what will be discussed at the Electronic Design Process Symposium in Monterey next Thursday and Friday. At EDPS Herb Reiter organized a session on FinFET, 3DIC and FD-SOI (sort of how many buzzwords can you get into one set of titles).… Read More

TLM Modeling Environment Goes Commercial

The most successful EDA companies typically choose a domain where they have deep knowledge, then serve a few leading-edge customers that are willing to work with a start-up in exchange for early access to that new technology. The theory is that if you can satisfy the leading-edge customer then you can also satisfy the rest of the … Read More