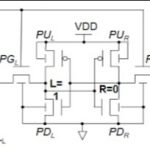

I’ve done SRAM and DRAM design before as a circuit designer from 1978-1986, but in 2016 there are so many more challenges to using 28nm and 14nm on FDSOI technology. One way to keep abreast of SRAM design is to read conference papers, so I just finished a paper from authors at STMicroelectronics and MunEDA presented at the IEEE… Read More

Tag: stmicroelectronics

In the Valley & thinking about FD-SOI for your next chip design? Epic (and free) symposium 13 April

If you’re in the chip biz in Silicon Valley, check out the SOI Consortium FD-SOI Symposium on April 13th in San Jose. They’ve been running these things since 2009, and I have to say that this one is the most comprehensive to date. Headliners include Cisco, Sony, NXP, SigmaDesigns, ARM, Ciena plus the big FD-SOI foundries,… Read More

Design and Optimization of Analog IP is Possible

Designing Analog IP is often referred to as a “black art”, something that only highly experienced craftsmen can produce using transistor-level techniques that aren’t shared outside of their closely held group of trusted co-workers. I’d like to suggest that Analog IP can be designed and optimized … Read More

IP-SoC Rebound in 2015 !

Going to IP-SoC every year since 2006, I have enjoyed the conference as it’s the only one 100% IP focused and a very good opportunity to network within this rather small ecosystem of IP vendors… but I must admit that, since 2012, the attendance tend to be lower than before. Because of the well-known “chicken & egg” theorem, low … Read More

28nm FD-SOI: A Unique Sweet Spot Poised to Grow

I have been silently watching STMicroelectronics pursuing FD-SOI technology since quite a few years. FinFET was anyway getting more attention in the semiconductor industry because of several factors involved. But from a technology as well as economic perspective there are many plus points with FD-SOI. I remember my debate,… Read More

FDSOI Cost Analysis – Part I

One of the most frequently discussed concerns regarding FDSOI adoption is the higher starting wafer cost compared to bulk technology. This discussion was also brought up after my earlier post,… Read More

Moving up Verification to Scenario Driven Methodology

Verification complexity and volume has always been on the rise, taking significant amount of time, human, and compute resources. There are multiple techniques such as simulation, emulation, FPGA prototyping, formal verification, post-silicon testing, and so on which gain prominence in different situations and at different… Read More

Design For Safety in Automotive Electronics

Do you remember how auto maker Toyota had to pay a $1.2 billion settlement in 2014 because some of their automotive models experienced sudden, unintended acceleration? That scenario has to be an engineer’s worst nightmare because something was missed during the design and testing of an automotive electronics system that… Read More

FD-SOI: a Gentle Introduction

Over the last couple of weeks, FD-SOI has been in the news with GlobalFoundries announcement of a 22nm FD-SOI process that will run in the Dresden Fab. Also, earlier in the week I talked to Thomas Skotnicki about the saga (and it is a saga) of how FD-SOI got from his PhD thesis to volume manufacturing and global deployment. But there … Read More

Thomas Skotnicki: FD-SOI 26 Years in the Making

It seems to be FD-SOI week yet again. I talked to Thomas Skotnicki this morning. He is the father of thin-box FD-SOI and its birth is an interesting story. The story began 26 years ago (so not quite as far back as the photo!).

Thomas is of Polish origins (he is actually Tomeczek) and grew up in Warsaw where he earned his PhD. In 1983 in Canterbury,… Read More