2016 will be a banner year for the System on Chip (SoC) industry. For the first time we will have leading edge SoCs (Apple, Qualcomm, Samsung) on the same manufacturing process enabling a true Apples to Apples comparison. Unfortunately, how we got there is being misrepresented by the media and analysts but that is Situation Normal… Read More

Tag: samsung

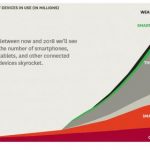

Meeting Demand as Fab Capacity is Stretched Again

Global semiconductor production capacity and its utilization level are key elements of the technology economy. During a panel at DAC in June Mentor Graphics posited that we are entering into a period where leading edge processes will be in high demand and also older nodes are seeing increasing demand due to Internet of Things designs… Read More

Make American Semiconductor Great Again!

As I watched the GOP debate between the top 10 candidates last week I asked myself which one of those men would I pick to help the United States stay competitive in the semiconductor industry. I’m saddened to say that the only candidate even remotely qualified for that conversation in my opinion is Donald Trump. Of course I backed Ross… Read More

China (and Cupertino) Are Killing Korea in Mobile

Samsung, #1 in the mobile phones based on unit shipments, has two big problems in mobile. Apple’s iPhone; and China in general and Huawei in particular in the Android world where they live. They have just announced their fifth quarter of decline. Revenue was down 8% year on year but operating profit declined 38%. They sold … Read More

A Key Aspect Missing for IoT to become NBT

The IoT (Internet of Things) is not one product, technology, segment, or market. It’s a combination of many things, many markets, and many technologies. However, it’s one thing that needs to connect everything together; edge device to gateway to cloud. That brings the complexity, how’s that possible amid large heaps of heterogeneous… Read More

UTBB SOI can scale down to 5nm says Skotnicki…

…and FinFET down to 3nm. This assertion is the result of extensive research work made by Thomas Skotnicki, ST Fellow and Technical VP, Disruptive Technologies, leading to numerous publications, like in 1988 in IEEE EDL or in 2008 in IEEE TED paper. I say extensive, I should also say long, very long, as it took almost 30 years for the… Read More

FD-SOI: a Gentle Introduction

Over the last couple of weeks, FD-SOI has been in the news with GlobalFoundries announcement of a 22nm FD-SOI process that will run in the Dresden Fab. Also, earlier in the week I talked to Thomas Skotnicki about the saga (and it is a saga) of how FD-SOI got from his PhD thesis to volume manufacturing and global deployment. But there … Read More

Apple Took All the Money

Apple has roughly 20% market share of the smartphone unit shipments. Android has pretty much all the rest with a tiny sliver for Microsoft Windows Phone, Blackberry, and Samsung’s Tizen. By any standard, Android is the highest volume operating system ever created. Famously, Microsoft makes more money on patent licenses… Read More

Who Needs to Lead at the 14, 10 and 7nm nodes

IBM recently disclosed a working 7nm test chip generating a lot of excitement in the semiconductor industry and also in the mainstream media. In this article I wanted to explore the 14nm, 10nm and 7nm nodes, the status of the key competitors at each node and what it may mean for the companies.

Apple Watch – A Great New Design, Needs More

During 52[SUP]nd[/SUP] DAC, there was a special session where a brand new Apple watch was opened and each of its components was shown with a brief description about it. I found this tear down session a great innovative idea coming from DAC organizers; actually two buzzing products, AppleWatch and DJI’s Phantom Drone were opened… Read More