By the time that your SoC comes back from the fab and you plugin it into a socket on a board for testing, it’s a little late in the cycle to start thinking about reliability concerns like: dynamic voltage drop, noise coupling, EM (Electro-Migration), self-heating, thermal analysis and ESD (Electro-Static Discharge). They… Read More

Tag: reliability

ANSYS Enters the League of 10nm Designs with TSMC

The way we are seeing technology progression these days is unprecedented. It’s just about six months ago, I had written about the intense collaboration between ANSYSand TSMCon the 16nm FinFET based design flow and TSMC certifying ANSYS tools for TSMC 16nm FF+ technology and also conferring ANSYS with “Partner of the Year” award.… Read More

Ensuring Safety Distinctive Design & Verification

In today’s world where every device functions intelligently, it automatically becomes active on any kind of stimulus. The problem with such intelligence is that it can function unfavorably on any kind of bad stimulus. As the devices are complex enough in the form of SoCs (which at advanced process nodes are more susceptible to … Read More

ANSYS Tools Shine at FinFET Nodes!

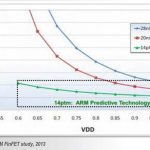

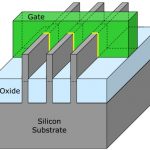

In the modern semiconductor ecosystem we are seeing rapid advancement in technology breaking past once perceived limits; 28nm, 20nm, 16-14nm, 10nm and we are foreseeing 7nm now. Double and multi-patterning are already being seen along with complex FinFET structures in transistors to gain the ultimate advantages in PPA from… Read More

Sidense overlays OTP on TSMC 16nm FinFET

Process shrinks, which have served us well for most of the Moore’s Law journey, are reaching their limits. For switching transistors, the biggest problems of leakage current and gate oxide vulnerability in planar MOSFETs have led the industry to new 3D microstructures such as FinFET. For non-volatile memory, the problem is generally… Read More

FinFET Design for Power, Noise and Reliability

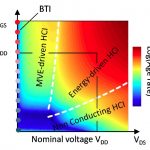

IC designers have been running analysis tools for power, noise and reliability for many years now, so what is new when you start using FinFET transistors instead of planar transistors? Calvin Chow from ANSYS (Apache Design) presented on this topic earlier in the summer through a 33 minutewebinar that has been archived. There is… Read More

IO Design Optimization Flow for Reliability in 28nm

User group meetings are a rich source of information for IC designers because they have actual designers talking about how they used EDA tools in their methodology to achieve a goal. Engineers at STMicroelectronicspresented at a MunEDAUser Group on the topic: I/O Design Optimization Flow For Reliability In Advanced CMOS Nodes.… Read More

Ensuring ESD Integrity

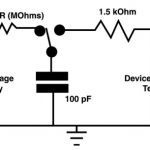

Electro Static Discharge (ESD) is a fact of life for IC designs and has been ever since electronics were first created and then started failing because of sudden, large currents flowing through the design caused by human, processing or machine contact. It’s just too expensive to layout an IC today, fabricate it, test for … Read More

Intel & Ansys Enable 14nm Chip Production

In the semiconductor industry, it feels great to hear about the process technology shrinking to lower nodes along with innovative transistor structures that offer major gains in PPA (Power, Performance and Area). However, it requires huge investment of capital, time and effort from foundries to conceptualize, prototype and… Read More

Five Things You Don’t Know About MunEDA

So first the one thing that you do know. MunEDA are based in Munich which makes them German. I have to confess that until I got involved helping them a bit with some marketing stuff that that was about all I knew about them too.

So now five things that you might not know:

1. MunEDA have a much wider customer list that you know and would even… Read More