Although semiconductor manufacturing has taken off with FinFET based process technology which provides lucrative payoffs on performance improvement, power reduction and area saving in devices for high density and high performance SoC demand of modern era, apprehensions remain about its reliability due to reduced noise … Read More

Tag: reliability

High Sigma Yield Analysis and Optimization at DAC

When I hear the phrase “high sigma” I think of the EDA vendor Solido, however at DAC on Monday I visited another EDA company called MunEDAthat has several products of interest to transistor-level IC designers. I was able to speak with three different people from MunEDA and here’s what I learned.… Read More

Sidense NVM IP clears TSMC9000 at 28nm

Maybe I’ve spent too many years whiffing solder flux fumes and absorbing doses of X-band radiation in anechoic chambers, but I’m a firm believer in the axiom: “Give me enough engineers, and I can get 10 of anything to work right, once.” We have to make this … fit into this … using only this stuff … is what legends are made of.… Read More

IC Power Noise Reliability for FinFET Designs

Reliability for ICs is a big deal because the last thing that you want to do is ship a new part only to find out later in the field that there are failures not being caught by testing. I’ve already had two consumer products fail this year because of probable reliability issues: My MacBook Pro with 16GB of RAM started rebooting caused… Read More

IC/Package/Board – Power, Noise and Reliability from ANSYS (Apache DA) at DAC

ANSYS acquired Apache Design Automation back in June 2011and three years later the name “Apache” is being subdued in favor of using just ANSYS. One thing that I noticed right away was a DACfocus on having actual ANSYS customers talk about their hands-on experience using the EDA tools. The following seven customers… Read More

Stop TDDB from getting through peanut butter

There are a few dozen causes of semiconductor failure. Most can be lumped into one of three categories: material defects, process or workmanship issues, or environmental or operational overstress. Even when all those causes are carefully mitigated, one factor is limiting reliability more as geometries shrink – and it… Read More

Managing Heat for System Reliability

In most of the electronic equipments, semiconductor chips are a major source of heat generation. And in semiconductor designs several hardware and software techniques are being used to contain power dissipation; a major cause for heat. However due to multiple functionality being squeezed into small form factors, we continue… Read More

Mission Critical Role of Unmanned Systems – How to fulfill?

Do we ever imagine what kind of severe challenges mission critical unmanned systems in air, land and underwater face? They are limited in space and size; have to be light in weight, flexible in different types of operations and at the same time rugged enough to work in extreme climatic conditions. That’s not enough; amidst these … Read More

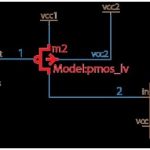

How to Simplify Complexities in Power Verification?

With multiple functionalities added into a single chip, be it a SoC or an ASIC, maintaining low power consumption has become critical for any design. Various techniques at the technology as well as design level are employed to accomplish the low power target. These include thinner oxides in transistors, different sections of … Read More

Reliability sign-off has several aspects – One Solution

Here, I am talking about reliability of chip design in the context of electrical effects, not external factors like cosmic rays. So, the electrical factors that could affect reliability of chips could be excessive power dissipation, noise, EM (Electromigration), ESD (Electrostatic Discharge), substrate noise coupling and… Read More