There are two ways to see how resistant your designs are to single-event errors (SEE). One is to take the chip or even the entire system and put it in a neutron beam and measure how many problems occur in this extreme environment. While that may be a necessary part of qualification in some very high reliability situations, it is also … Read More

Tag: reliability

Power and Reliability Sign-off – A must, but how?

At the onset of SoCs with multiple functionalities being packed together at the helm of technologies to improve upon performance and area; power, which was earlier neglected, has become critical and needs special attention in designing SoCs. And there comes reliability considerations as well due to multiple electrical and … Read More

System Reliability Audits

How reliable is your cell-phone? Actually, you don’t really care. It will crash from time to time due to software bugs and you’ll throw it away after two or three years. If a few phones also crash due to stray neutrons from outer space or stray alpha particles from the solder balls used in the flip-chip bonding then nobody… Read More

Today’s Program is Brought To You by the Letter A

What do nVidia, Freescale and GlobalFoundries have in common? They are semiconductor companies? They are ARM licensees? They are doing 28nm chips? They all have the letter ‘a’ in their names?

All true, but that’s not what I was thinking of. But the letter ‘a’ is a clue since Apache (and Ansys) begin with ‘a’. All three companies have… Read More

10 years, 100,000 miles, or <1 DPM

Auto makers have historically been accused of things like planned obsolescence – redesigning parts to make repairs painfully or even prohibitively expensive – and the “warranty time-bomb”, where major systems seem to fail about a week after the warranty expires. Optimists would chalk both those up to relentless innovation,… Read More

SOCFIT, Circuit Level Soft Error Analysis

I blogged recently about reliability testing with high energy neutron beams. This is good for getting basic reliability data but it is not really a useful tool for worrying about reliability while the chip is still being designed and something can be done about it.

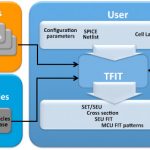

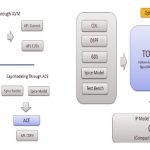

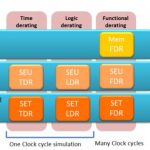

That is where IROC Technologies SOCFIT tool comes in. It takes all… Read More

How to Blast Your Chip with High Energy Neutron Beams

So you want to know how reliable your chips are and how susceptible they are to single event effects (SEEs) where a neutron or an alpha particle causes a storage element (flop or memory cell) to flip in a way that alters the behavior of the device. There are two ways a particle hitting a device might not cause a problem. Firstly, the particle… Read More

Cell Level Reliability

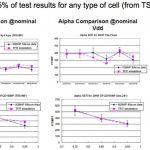

I blogged last month about single event effects (SEE) where a semiconductor chip behaves incorrectly due to being hit by an ion or a neutron. Since we live on a radioactive planet and are bombarded by cosmic rays from space, this is a real problem, and it is getting worse at each process node. But just how big of a problem is it?

TFIT is … Read More

Reliability is the New Power

It has be come a cliche to say that “power is the new timing”, the thing that keeps designers up at night and drives the major architectural decisions in big SoCs. Nobody is saying it yet but perhaps “reliability is the new power” will be tomorrow’s received wisdom.

I talked to Adrian Evans of IROCTech… Read More

We Live on a Radioactive Planet

Often as we move down the process node treadmill, new challenges appear that we didn’t really have to worry about before. Often, these challenges require addressing at a number of different levels: the process, the cell libraries, the design, the EDA tools that we use.

One well known example is the problem of metal migration.… Read More