You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

L.C. leads efforts in design enablement, ensuring that the company can meet the diverse and evolving requirements of its global customer base. Prior to this, he headed the Design and Technology Platform organization starting in 2018.

Since joining TSMC in 2000, Dr. Lu has held multiple leadership positions in design services.… Read More

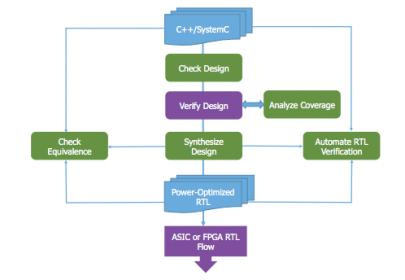

Register Transfer Level (RTL) is a crucial and valuable concept in digital hardware design. Over the years, it has played a fundamental role in enabling design of complex digital chips. By abstracting away implementation details and providing a clear description of digital behavior, RTL has contributed significantly to the… Read More

I wrote earlier about managing service-level risk in SoC design, since the minimum service level a system can guarantee under realistic traffic is critical to OEM guarantees of dependable system performance. An ABS design which might get bogged down in traffic under only 0.1% of scenarios is of no use to anyone. That said, meeting… Read More

Performance, Power and Area (PPA) metrics are the driving force in the semiconductor market and impact all electronic products that are developed. PPA tradeoff decisions are not engineering decisions, but rather business decisions made by product companies as they decide to enter target end markets. As such, the sooner a company… Read More

Performance, Power and Area (PPA) are the commonly touted metrics in the semiconductor industry placing PPA among the most widely used acronyms relating to chip development. And rightly so as these three metrics greatly impact all electronic products that are developed. The degree of impact depends of course on the specific … Read More

There has been a lot written about artificial intelligence/machine learning (AI/ML) and its application in the Cadence digital design flow. Most recently, I covered significant verification efficiency improvements in Xcellium ML. A recent digital-themed white paper from Cadence takes a broader look at the impact of ML on… Read More

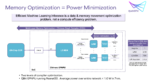

I’m on a mini-roll on the subject of high-level design for ML-based systems. No complaints from me, this is one of my favorite domains and is certainly a hot area; it’s great to that EDA vendors are so active in advancing ML-based design. Here I want to talk about the Catapult HLS flow for use in ML design.

Since I’ve covered the ML topic… Read More

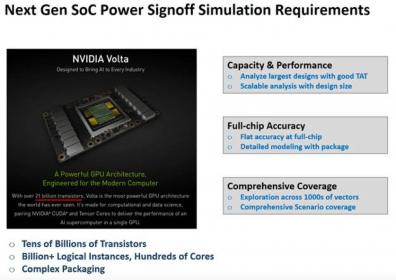

Want to know how NVIDIA signs off on power integrity and reliability on mega-chips? Read on.

PPA over-design has repercussions in increased product cost and potential missed schedules with no guarantee of product success. Advanced SoCs pack more functionality and performance resulting in higher power density, but traditional… Read More

To paraphrase an Austen line, it is a truth universally acknowledged that implementation, power intent and design hierarchy don’t always align very well. Hierarchy is an artifact of legacy structure, reuse and division of labor, perhaps well-structured piecewise for other designs but not necessarily so for the design you now… Read More

If you are building an advanced SoC, you know that you’re going to need a lot of embedded memory. Unless this is your first rodeo, you also know that which memories you choose can have a huge impact on Power, Performance and Area (PPA) and, for some applications, Energy (power integrated over time), Temperature and Reliability. Which… Read More