Using chiplets is an emerging trend well-covered at #62DAC and they even had a dedicated Chiplet Pavilion, so I checked out the presentation from Dan Slocombe, Design Engineering Architect in the Compute Solutions Group at Cadence. In a short 20 minutes Dan managed to cover a lot of ground, so this blog will summarize the key points.… Read More

Tag: innovus

What’s New with Cadence Virtuoso?

It was back in 1991 that Cadence first announced the Virtuoso product name, and here we are 32 years later and the product is alive and doing quite well. Steven Lewis from Cadence gave me an update on something new that they call Virtuoso Studio, and it’s all about custom IC design for the real world. In those 32 years we’ve… Read More

EDA Flows for 3D Die Integration

Background

The emergence of 2.5D heterogeneous die integration using a silicon (or organic) interposer has enabled unique system architectures. The term “More than Moore” has been used to describe the circuit density and cost advantages of leveraging multiple die in the package, the die potentially in different process technologies. … Read More

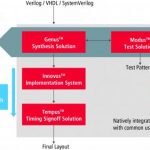

Cadence Defines a New Signoff Paradigm with Tempus PI

Semiconductor technology advances have a way of rewriting the rule book. As process geometries shrink, subtle effects graduate to mainstream problems. Performance curves can become inverted. And no matter what else occurs, low power demands are constantly reducing voltage and design margins along with it. Sometimes these… Read More

The Complexity of Block-Level Placement @ 56thDAC

The recent Design Automation Conference in Las Vegas was an indication of how the electronics industry is evolving. In its formative years, DAC was focused on the fundamental algorithms emerging from academic research and industrial R&D, that enabled the continuation of the Moore’s Law complexity curve. (Indeed, the… Read More

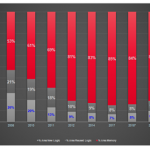

IoT Designs Beginning to Shift to 7nm: Promises Upside for Cadence Physically-Aware Design Flow

Until recently, ICs at bleeding edge nodes like 7nm technology from foundries like TSMC were mostly targeted for high-performance-computing (HPC) and mobile applications or possibly high radix switches that needed the increased performance of advanced nodes. The momentum of Moore’s law and Moore-than-Moore saw foundries… Read More

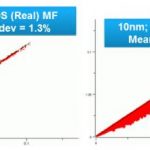

Extraction Features for 7nm

Frequent Semiwiki readers are familiar with the importance of close collaboration between the foundries and EDA tool developers, to provide the crucial features required by new process nodes. Perhaps the best illustration of the significance of this collaboration is the technical evolution of layout parasitic extraction.… Read More

The CDNLive Keynotes

I’m developing a taste for user-group meetings. In my (fairly) recently assumed role as a member of the media, I’m only allowed into the keynotes, but from what I have seen, vendors work hard to make these fresh and compelling each year through big-bang product updates and industry/academic leaders talking about their work in bleeding-edge… Read More

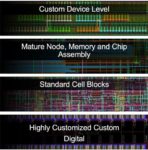

Digital Design Trends – A Cadence Perspective

I talked with Paul Cunningham (VP front-end digital R&D) at CDNLive recently to get a Cadence perspective on digital design trends. He sees needs from traditional semiconductor companies evolving as usual, with disruption here and there from consolidation. But on the system side there is explosion in demand – for wearables,… Read More

Cadence Adds New Dimension to SoC Test Solution

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More