At the recent SPIE Advanced Lithography + Patterning Conference, Mark Phillips from Intel gave an insightful update on the status of the introduction of the 0.55 high numerical aperture extreme ultraviolet lithography technology. Mark went so far as to assert that the development progress toward high-NA EUV would support … Read More

Tag: euv

Demonstration of Dose-Driven Photoelectron Spread in EUV Resists

As a consequence of having a ~13.5 nm wavelength, EUV photons transfer ~90% of their energy to ionized photoelectrons. Thus, EUV lithography is fundamentally mostly EUV photoelectron lithography. The actual resolution becomes dependent on photoelectron trajectories.

Photoelectron trajectories in EUV lithography were… Read More

Has KLA lost its way?

-KLA has another great QTR in face of overwhelming demand

-Supply chain issues obliterated by backlog

-Longer term technology leadership concerns are increasing

-We see limited upside near term & remain cyclically cautious

Another great quarter- demand remains super strong

KLA’s performance remains great as does… Read More

Adding Random Secondary Electron Generation to Photon Shot Noise: Compounding EUV Stochastic Edge Roughness

The list of possible stochastic patterning issues for EUV lithography keeps growing longer: CD variation, edge roughness, placement error, defects [1]. The origins of stochastic behavior are now well-known. For a given EUV photon flux into the resist, a limited fraction are absorbed. Since the absorption is less than 5% affected… Read More

Chip Enabler and Bottleneck ASML

-ASML reported an “in line” Q1- Orders remain super strong

-Ongoing supply chain issues will limit growth and upside

-ASML targets 2025 for supply fixes- We are not so sure

-Intel, TSMC, Samsung won’t be able to build all fabs they plan

ASML has “In linesh” Q1, orders still off the charts

ASML reported… Read More

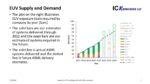

Intel and the EUV Shortage

In my “The EUV Divide and Intel Foundry Services” article available here, I discussed the looming EUV shortage. Two days ago, Intel announced their first EUV tool installed at their new Fab 34 in Ireland is a tool they moved from Oregon. This is another indication of the scarcity of EUV tools.

I have been tracking EUV system production… Read More

EUV Resist Absorption Impact on Stochastic Defects

Stochastic defects continue to draw attention in the area of EUV lithography. It is now widely recognized that stochastic issues not only come from photon shot noise due to low (absorbed) EUV photon density, but also the resist material and process factors [1-4].

It stands to reason that resist absorption of EUV light, which is … Read More

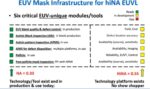

DUV, EUV now PUV Next gen Litho and Materials Shortages worsen supply chain

-New PUV light source will push litho into Angstrom Era

-Rare earth elements shortages add to supply chain woes

-Could strategic wafer reserve releases lower memory pricing

-Can we cut off/turn off Russian access to chip equipment?

DUV, EUV and now “PUV” to become next generation lithography

Lithography is the locomotive… Read More

The EUV Divide and Intel Foundry Services

The EUV Divide

I was recently updating an analysis I did last year that looked at EUV system supply and demand, while doing this I started thinking about Intel and their Fab portfolio.

If you look at Intel’s history as a microprocessor manufacturer, they are typically ramping up their newest process node (n), in volume production… Read More

CEO Interview: Aki Fujimura of D2S

Curvilinear Design Primer for Design, Packaging Communities

This interview was done by Bob Smith, Executive Director, ESD Alliance, a SEMI Technology Community.

Previously, Fujimura served as CTO at Cadence Design Systems and returned to Cadence for the second time through the acquisition of Simplex Solutions where he was… Read More