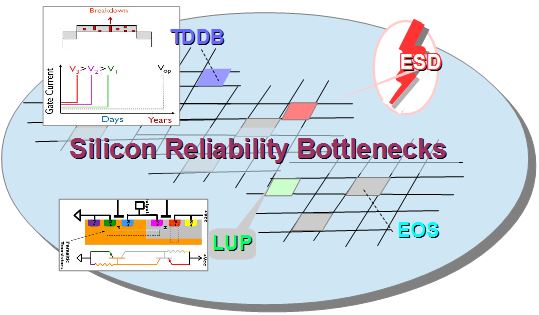

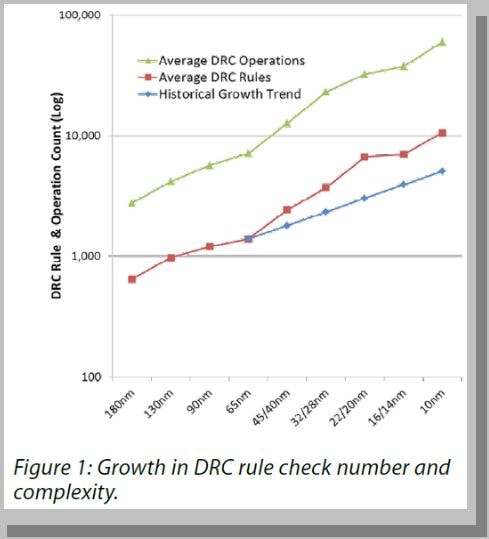

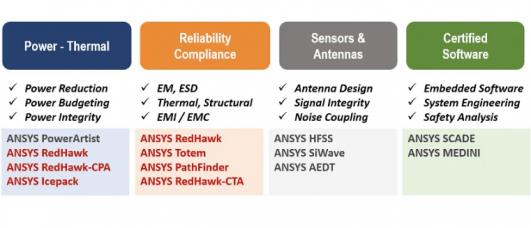

Advanced process technology offers both device and interconnect scaling for increased design density and higher performance while invoking also significant implementation complexities. Aside from the performance, power and area (PPA) aspects, designer is getting entrenched with the need of tackling more reliability … Read More

Tag: esd

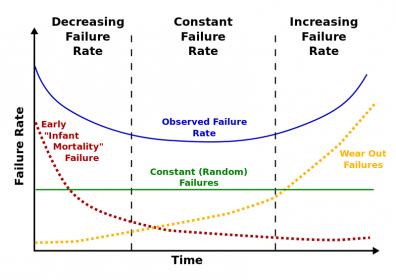

Stress and Aging

These failings aren’t just a cross we humans bear; they’re also a concern for chips, particularly in electrical over-stress (EOS) and aging of the circuitry. Such concerns are not new, but they are taking on new urgency given the high reliability and long lifetime expectations we have for safety-critical components in cars and… Read More

Robust Reliability Verification – A Critical Addition To Baseline Checks

Design process retargeting is acommon recurrence based on scaling orBOM(Bill-Of-Material) cost improvement needs. This occursnot only with the availability of foundry process refresh to a more advanced node,but also to any new derivative process node tailored towards matching design complexity, power profile or reliability… Read More

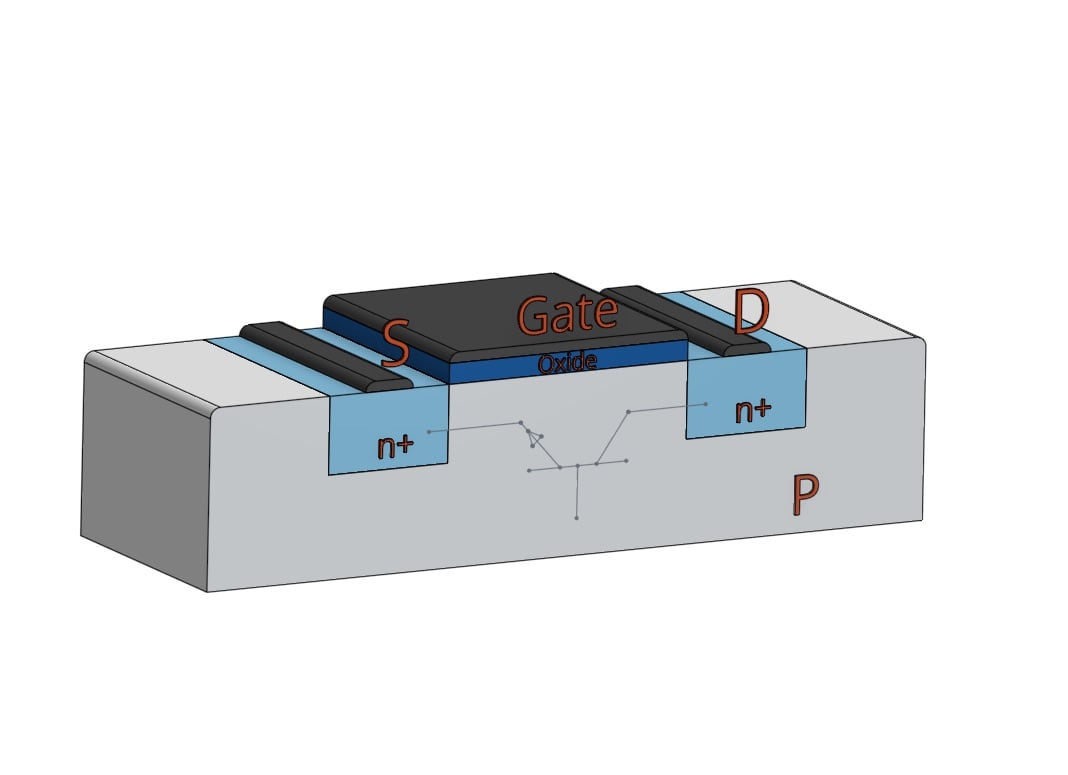

Snapback behavior determines ESD protection effectiveness

Terms like avalanche breakdown and impact ionization sound like they come from the world of science fiction. They do indeed come from a high stakes world, but one that plays out over and over again here and now, on a microscopic scale in semiconductor devices – namely as part of electrostatic discharge (ESD) protection. Semiconductor… Read More

Reliability Signoff for FinFET Designs

Ansys recently hosted a webinar on reliability signoff for FinFET-based designs, spanning thermal, EM, ESD, EMC and aging effects. I doubt you’re going to easily find a more comprehensive coverage of reliability impact and analysis solutions. If you care about reliability in FinFET designs, you might want to check out this webinar.… Read More

TechCon: See ANSYS and TSMC co-present

ANSYS and TSMC will be co-presenting at ARM TechCon on Multiphysics Reliability Signoff for Next Generation Automotive Electronics Systems. The event is on Thursday October 26th, 10:30am-11:20am in Grand Ballroom B.

You can get a free Expo pass which will give you access to this event HERE and see the session page for the event … Read More

Webinar: Signoff for Thermal, Reliability and More in Advanced FinFET designs

In automotive applications, advanced FinFET processes are great for high levels of integration and low power. But they also present some new challenges in reliability signoff. Ansys will be hosting a webinar to highlight the challenges faced by engineers trying to ensure thermal, electromigration (EM) and electrostatic discharge… Read More

Simulating ADAS

Simulation is a broad technique spanning certainly digital logic and circuit simulation but also methods beyond these which are particularly relevant to ADAS design. In fact, much of the design of full ADAS systems begins and ends with these types of modeling. This is in part due to the need fully validate integrity and reliability… Read More

Stressed out about Electrostatic Discharge (ESD) or Electrical Overstress (EOS)?

Do not lose sleep worrying that your integrated circuits might fail during EOS/ESD events. Join us for the 38th annual EOS/ESD Symposium in Anaheim, CA in September. Experts on the field will address the latest research on EOS and ESD in the rapidly changing world of electronics.

As electronics continue to become commonplace in… Read More

Integrity and Reliability in Analog and Mixed-Signal

In the largest and fastest growing categories in electronics – mobile, IoT and automotive – analog is playing an increasingly important role. It’s important in delivering high integrity power and critical signals to the design though LDO regulators and PLLs, in managing high speed interfaces like DDR and SERDES, in interfacing… Read More