You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Everyone has heard the expression, “Half the job is having the right tool.” In the case of FPGA-based prototyping, however, the right tool for the job is only the beginning. What teams really need to think through is what exactly should be done with an FPGA-based prototyping tool?

The obvious answer is prototyping an SoC, pre-silicon.… Read More

It’s less than four weeks to go at DAC 2015 and the program is final now. So I started investigating new technologies, trends, methodologies, and tools that will be unveiled and discussed in this DAC. In the hindsight of the semiconductor industry over the last year, I see 14nm technologies in the realization stage and 10nm beckoning… Read More

Xilinx users will welcome the brand-new release of Vivado Design Suite 2015.1. For openers, device support for the latest FPGAs in the UltraScale family – XCVU440, XCVU190, and XCVU125 – has been added in the release, and early access code for the XCVU160 is available from a local Xilinx FAE. Installation has been streamlined, … Read More

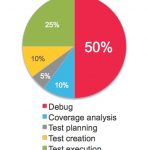

Sure, design engineers can get more attention than verification engineers, but the greater number of verification engineers on SoC projects means that the verification task is a bigger bottleneck in a schedule than pure design work. A recent survey conducted at Cadence shows how verification effort can be divided into several,… Read More

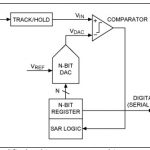

Multiple processor cores are now a given in SoCs. Grabbing IP blocks and laying them in a multicore design may be the easy part. While verification is extremely important, it is only the start – obtaining real-world performance depends on the combination of multicore hardware and actual application software. What should engineers… Read More

SMIC (Semiconductor Manufacturing International Corporation) is a China-based foundry with technology ranging from 0.35 micron to 28 nm, and we’ve blogged about them before on SemiWiki. I’ve been reading about SMIC recently because they created a technical presentation for the MunEDA Technical Forum Shanghai… Read More

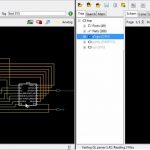

In today’s SoC world where multiple analog and digital blocks along with IPs at different levels of abstractions are placed together on a single chip, debugging at all levels becomes quite difficult and clumsy. While one is working at the top level and needs to investigate a particular connection at an intermediate hierarchical… Read More

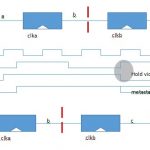

Multiple clock domains in FPGAs have simplified some aspects of designs, allowing effective partitioning of logic. As FPGA architectures get more flexible in how clock domains, regions, or networks are available, the probability of signals crossing clock domains has gone way up.… Read More

One of the big challenges with modern SoCs is that they have a complex software component as well as the hardware itself being complex. Some aspects of the hardware can be debugged independently of the software and vice versa, but often it is not immediately clear whether the source of a problem is hardware, software or some interaction… Read More

Integration is often an underrated attribute of good tools, compared to raw performance and technology. But these days integration is differentiation (try telling that to your calculus teacher). Today at DVCon Synopsys announced Verification Compiler which integrates pretty much all of Synopsys’s verification technologies… Read More