High-speed digital (HSD) designers have long tested the limits of realizable speed. GHz frequencies are now the norm, and multi-level signaling is pushing rates higher while the long-awaited transition to optical signaling and even higher rates looms ever closer. Power density is also climbing, and data-hungry applications… Read More

Tag: co-simulation

100G/200G Electro-Optical Interfaces: The Future for Low Power, Low Latency Data Centers

Electrical copper interconnects, once the backbone of data center networks, are facing growing challenges. Rapid expansion of AI and ML applications is driving a significant increase in cluster sizes within data centers, resulting in substantial demands for faster I/O capabilities. While the surge in I/O requirements is … Read More

Unlock first-time-right complex photonic integrated circuits

The capacity and energy efficiency challenges from the growing appetite for high-speed data along with advanced applications such as LIDAR and quantum computing are driving demand for increasingly large-scale photonic integrated circuits (PIC). With an ever-increasing number of components on a single photonic chip, manual… Read More

Aldec Adds Simulation Acceleration for Microchip FPGAs

Despite the fact that FPGA based systems make it easy to add ‘hardware in the loop’ for verification, the benefits of HDL and gate level simulation are critical for finding and eliminating issues and bugs. The problem is that software simulators can require enormous amounts of time to run full simulations over sufficient time intervals… Read More

Webinar on Transient Simulation of Power Transistors in Converter Circuits

Magwel is offering a webinar that takes a deeper look at how Power Transistors can be more accurately simulated in converter circuits to provide extremely accurate information about switching efficiency. DC converter circuit efficiency has a big effect on the battery life of mobile devices and can affect performance and efficiency… Read More

Aldec Swings for the Fences

In today’s fast-moving technology markets, companies who are prepared to step up to opportunity can break out of traditional bounds to become players in bigger and fast-growing markets. It looks to me like Aldec is putting itself on that path. They have announced an end-to-end hardware/software co-verification solution… Read More

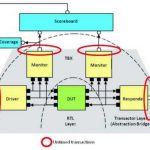

Striving for one code base in accelerated testbenches

Teams buy HDL simulation for best bang for the buck. Teams buy hardware emulation for the speed. We’ve talked previously about SCE-MI transactors as a standardized vehicle to connect the two approaches to get the benefits of both in an accelerated testbench – what else should be accounted for?… Read More

Aldec extends FPGA and ASIC flows at DAC

Aldec tools and services have long been associated with FPGA designs. As FPGAs have evolved toward more RTL-based designs, the similarities between a modern FPGA verification flow and an ASIC verification flow often leave them looking virtually the same. … Read More

Aldec reprograms HES7 for AXI4 speed

FPGA-based prototyping firms are all grappling with the problem of higher speed connectivity between a development host and their hardware. Aldec is announcing their solution at DVCon 2016, turning to an AMBA AXI4 interface bridged into a host with PCIe x8.

Faster host interfaces deliver dual benefits in FPGA-based prototyping.… Read More

Simulating to a fault in automotive and more

We’re putting the finishing touches on Chapter 9 of our upcoming book on ARM processors in mobile, this chapter looking at the evolution of Qualcomm. One of the things that made Qualcomm go was their innovative use of digital simulation. First, simulation proved out the Viterbi decoder (which Viterbi wasn’t convinced had a lot … Read More