Leading edge SoC designs can contain billions of transistors, cost over $10M to design, and take over 18 months to deliver, but not all SoCs require that much complexity, cost and time. In fact, there is a growing class of SoC designs that integrate the popular ARM Cortex-M0 processor along with analog blocks that work with sensors… Read More

Tag: analog

Qorvo and KeySight to Present on Managing Collaboration for Multi-site, Multi-vendor RF Design

Over the last several weeks I’ve been having a lot of discussions with colleagues around IP reuse and design data management. This led me to a discussion with Ranjit Adhikary, Marketing Vice President for ClioSoft.

ClioSoft is best known for their design collaboration software platform called SOS. They also sell an enterprise… Read More

Analog, Low-power Optimization at SMIC

Talking with actual IC designers is always fascinating to me, because these engineers are the unsung heroes that enable our modern day world of consumer and industrial electronics. Too often we only hear from the CEO or other C-level executives in the press about their own companies, products, services and vision. I recently had… Read More

Mentor DefectSim Seen as Breakthrough for AMS Test

For decades, digital test has been fully automated including methodologies and automation for test pattern generation, grading and test time compression. Automation for analog and mixed-signal (AMS) IC test has not however kept pace. This is troubling as according to IBSapproximately 85% of SoC design starts are now AMS designs.… Read More

Can one flow bring four domains together?

IoT edge device design means four domains – MEMS, analog, digital, and RF – not only work together, but often live on the same die (or substrate in a 2.5D process) and are optimized for power and size. Getting these domains to work together effective calls for an enhanced flow.

Historically, these domains have not played together … Read More

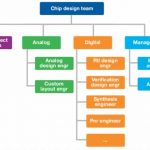

Organizing Data is First Step in Managing AMS Designs

Efficient collaboration is essential to meeting tight chip design schedules. In analog and mixed signal (AMS) design, collaboration has many facets. Design tools are usually specific to roles, and handoffs are numerous, especially when moving a design to a foundry. … Read More

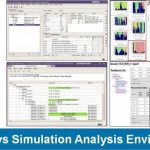

Synopsys’ New Circuit Simulation Environment Improves Productivity — for Free

When technology advances, complexities increase and data size becomes unmanageable. Fresh thinking and a new environment for automation are needed to provide the required increase in productivity. Specifically in case of circuit simulation of advanced-node analog designs, where precision is paramount and a large number… Read More

Synopsys Vision on Custom Automation with FinFET

In an overwhelmingly digital world, there is a constant cry about the analog design process being slow, not automated, going at its own pace in the same old fashion, and so on. And, the analog world is not happy with the way it’s getting dragged into imperfect automation so it can be more like the digital world. True, the analog world… Read More

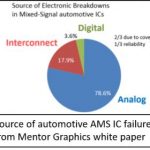

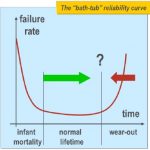

Predicting Lifetime of Analog ICs

With the increase of transistors per unit area, high density interconnects and manufacturing variability at lower nodes, the electronic devices have become more vulnerable to failures. The devices that operate under extreme conditions such as automotive devices that operate at high temperatures need to be robust enough to… Read More

Unlock the Key to Ultra-Low Power Design

We have been hearing about low power for a long time. Fortunately, low power chip operation has come about through a large number of innovations. Key among these is clock gating, frequency and voltage scaling, managing leakage with lower threshold voltage, HKMG, and many other techniques. But we are entering the age of ultra low… Read More