On October 10, I attended another Cadence Summit, this one titled the Cadence Mixed-Signal Technology Summit. Recently, I had written about the Cadence Silicon Verification Summit. The verification event was the first of its kind, and I thought it had terrific content. Being more of a digital guy myself, I was unaware that Cadence… Read More

Tag: analog

Bringing Sanity to Analog IC Design Verification

Two weeks ago I blogged about analog verification and it started a discussion with 16 comments, so l’ve found that our readers have an interest in this topic. For decades now the Digital IC design community has used and benefited from regression testing as a way to measure both design quality and progress, ensuring that first… Read More

GlobalFoundries in Singapore

I hosted a webinar today for GlobalFoundries. Yes, I know that today was TSMC’s Technology Symposium, we weren’t that smart when we picked the date. It was basically a “fireside chat” with me as the moderator asking the questions and Paul Colestock and Aabid Husain as my guests. We actually did it at Cadence… Read More

GF, Analog and Singapore

The world is analog and despite enormous SoCs in the most leading-edge process node being the most glamorous segment of the semiconductor industry, it turns out that one of the fastest growing segments is actually analog and power chips in older process technologies. Overall, according to Semico, analog and power ICs, including… Read More

How accurate are AMS Behavioral Models?

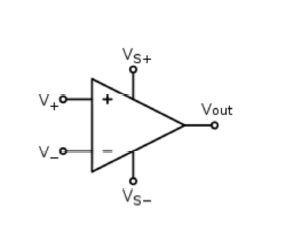

You often hear the mantra that Analog Mixed-Signal (AMS) behavioral models are inaccurate. It is repeated so often that it starts to morph into “AMS models are inherently inaccurate”. This is not true.

Source: Wikipedia

… Read More

Hybrids on BeO then, 3D-IC in silicon now

Once upon a time (since every good story begins that way), I worked on 10kg, 70 mm diameter things that leapt out of tubes and chased after airplanes and helicopters. The electronics for these things were fairly marvelous, in the days when surface mount technology was in its infancy and having reliability problems in some situations.… Read More

Cadence Mixed Signal Technology Summit

Yesterday I attended some of the Cadence mixed-signal technology summit. The day ended with a panel session on Are We Closing the Gap Yet in Mixed-signal Design? Richard Goering moderated. The panelists were all mixed signal experts:

- Nayaz Khan of Maxim

- Nishant Shah of Broadcom

- Shiv Sikand of IC Manage

- Bill Meier of Texas Instruments

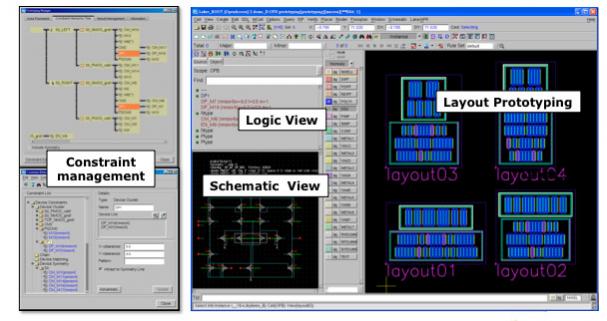

Laker Analog Prototyping

Over the years many attempts have been made to increase the level of automation in analog design. Most of these have not been especially successful. Probably part of the reason was inadequate technology but also there is an attitude that “real” analog designers design polygons on the bare silicon. I think two things… Read More

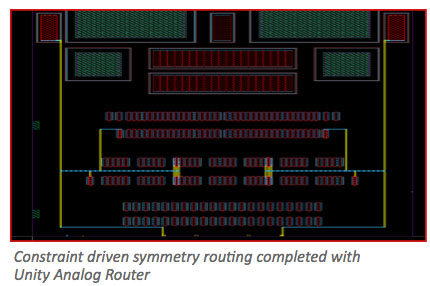

After Planning Comes Implementation for Pulsic

Automation for digital design has been mainstream for a couple of decades but place and route for analog is still in its infancy. Many attempts have been made over the years to automate analog design in one way and another, the bodies are piled up on the hillside. Much analog design is still largely done with custom layout and circuit… Read More

The Biggest EDA Company You’ve Never Heard Of

There’s this EDA company. They have over 100 tapeouts. They have a $28M in funding. They have 250 people. And you’ve never heard of them. Or at least I hadn’t.

They are ICScape. They started in 2005 with an investment from Acorn Campus Ventures and delivered their first product, ClockExplorer, in 2007 and their… Read More