The Internet of Things (IoT) is creating urgent demand for a new generation of analog/mixed-signal (AMS) designs, some of which also contain MEMs. To efficiently create the myriad of AMS devices at the edge of the IoT requires a design environment that is affordable and easy to use, but powerful enough to create the widely diverse… Read More

Tag: ams

Apple Watch – A Great New Design, Needs More

During 52[SUP]nd[/SUP] DAC, there was a special session where a brand new Apple watch was opened and each of its components was shown with a brief description about it. I found this tear down session a great innovative idea coming from DAC organizers; actually two buzzing products, AppleWatch and DJI’s Phantom Drone were opened… Read More

Bijan Kiani Talks Synopsys Custom Layout and More

Last week I sat down and talked to Bijan Kiani of Synopsys. He has marketing responsibility for design implementation products at Synopsys spanning digital, custom and analog mixed signal (AMS).

He was born in Iran and after high school he moved to the UK. He got his PhD degree from University of Edinburgh. It turns out that I was doing… Read More

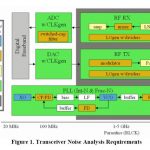

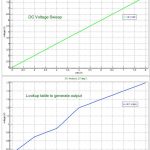

Full Spectrum Analog FastSPICE Useful for RF Designs on Bulk CMOS

It has been about a year since the acquisition of Berkeley Design Automation by Mentor Graphics. Berkeley was doing quite well in the somewhat crowded SPICE simulator market. In many respects they broke new ground for high speed and accurate SPICE simulators. Since the acquisition we know that former Berkeley executives are now… Read More

STMicro to Showcase Turnkey NFC Design at MWC

Near-field communication (NFC) technology is finally realizing its potential, thanks to the impetus provided by Apple Pay, and it’s becoming evident from the pre-Mobile World Congress (MWC) buzz coming from several makers of chips, smartphones and wearable devices.

Among the companies displaying NFC products at the 2015 … Read More

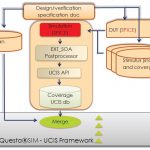

Coverage Driven Analog Verification

Ad hoc digital design verification approaches ran out of steam at least a decade ago when designs got intractably large to make it feasible to keep track of everything with pen and paper and excel. But analog design has remained largely ad hoc to this day. The designer runs spice, looks at the waveforms that come out and decide whether… Read More

Coverage Driven Verification for Analog?

We know there is a big divide between analog and digital design methodologies, level of automation, validation and verification processes, yet they cannot stay without each other because any complete system on a chip (SoC) demands them to be together. And therefore, there are different methodologies on the floor to combine analog… Read More

Design & EDA Collaboration Advances Mixed-Signal Verification through VCS AMS

Last week it was a rare opportunity for me to attend a webinar where an SoC design house, a leading IP provider and a leading EDA tool provider joined together to present on how the tool capabilities are being used for advanced mixed-signal simulation of large designs, faster with accuracy. It’s always been a struggle to combine design… Read More

AMS Panel: Micronas, Infineon, AMD, STMicro

Synopsyshosted an AMS Luncheon panel today at DACin the Westin Hotel and invited four customers to talk about their actual design challenges and experiences. I’ve typed up my notes from this event.… Read More

Teach Yourself Silvaco

In the dim and distant past, if you wanted to learn how to use a particular EDA tool then you would go on a training course. This would often be multiple days and often a significant dollar investment too. For most EDA companies, that option still exists and the big 3 have quite extensive training catalogs.

But nowadays it is often easier… Read More