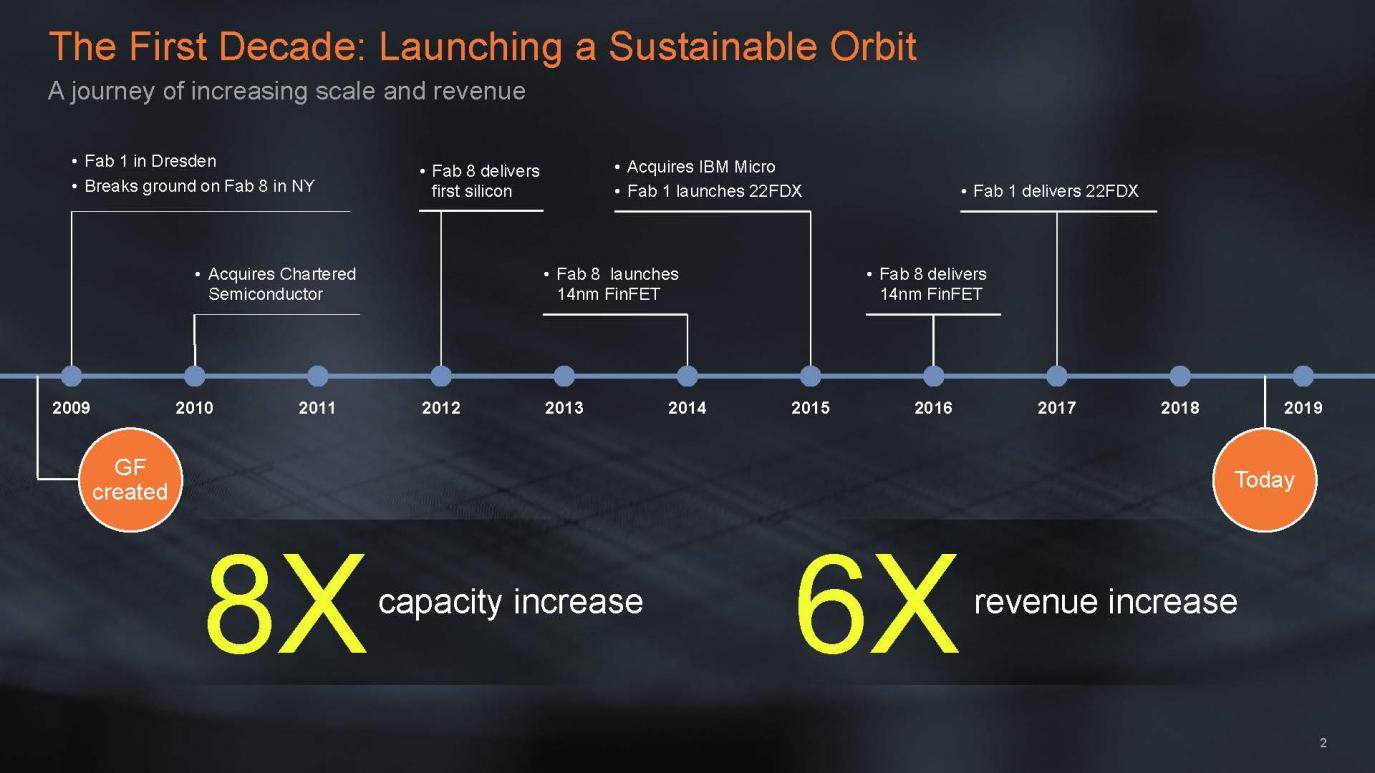

GLOBALFOUNDRIES (GF) recently announced they were abandoning 7nm and focusing on “differentiated” foundry offerings in a move our own Dan Nenni described as a “pivot”, a description GF appears to have embraced. Last week GF held their annual Technology Conference and we got to hear more about the pivot from new CEO Tom Caulfield… Read More

Tag: 7nm

IEDM Preview 2018

The International Electron Devices Meeting (IEDM) is one of the premier technical conferences covering semiconductor technology and is a must attend event. This years conference will be held December 1[SUP]st[/SUP] through 5th, 2018 at the Hilton San Francisco Union

Square hotel.… Read More

GloFo dropping out of 7NM race?

Could this be more bad news for semicap spend? Negative for US chip independence & AMD costs ? Rumors of Global Foundries dropping out of the 7NM race have been increasing rapidly. What could be a fatal blow to the GloFo 7NM program was AMD deciding to go with TSMC for 7NM first for one product and finally for its next generation CPUs.… Read More

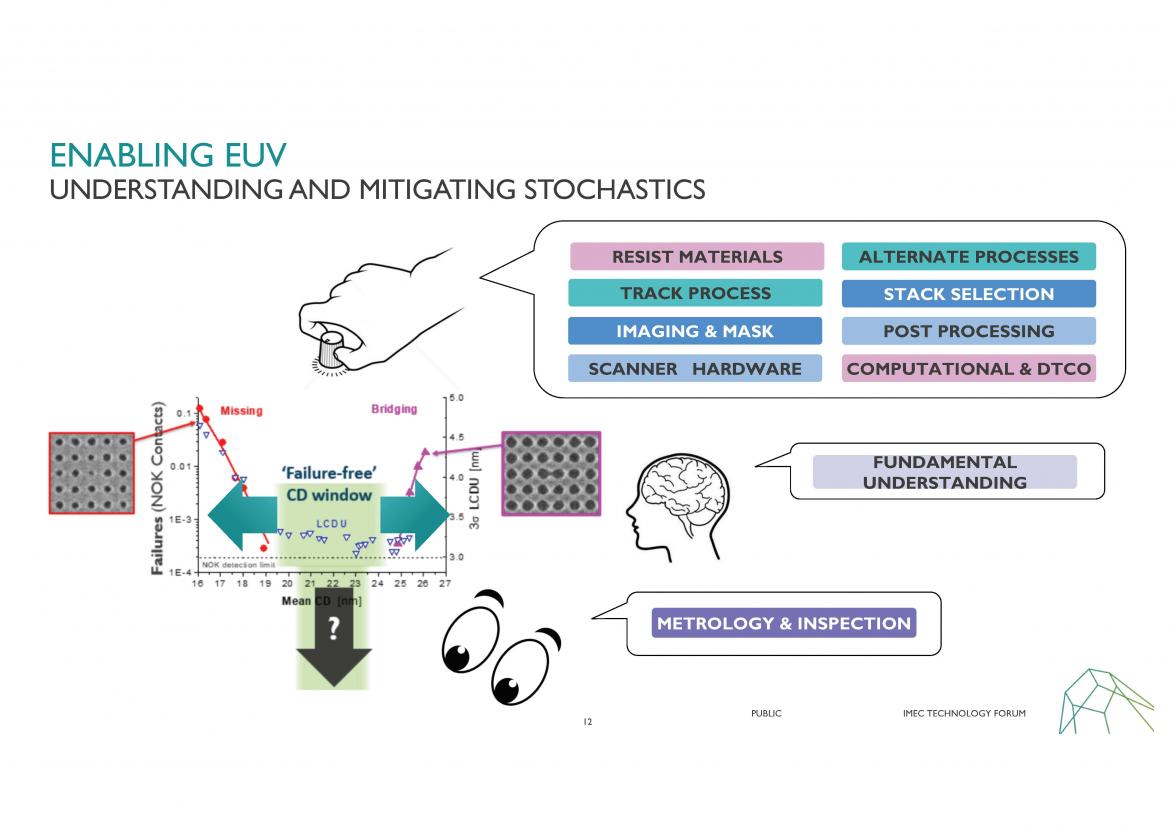

SEMICON West – Leading Edge Lithography and EUV

At SEMICON West I attended the imec technology forum, multiple Tech Spot presentations and conducted a number of interviews relevant to advanced lithography and EUV. In this article I will summarize what I learned plus make some comments on the outlook for EUV.… Read More

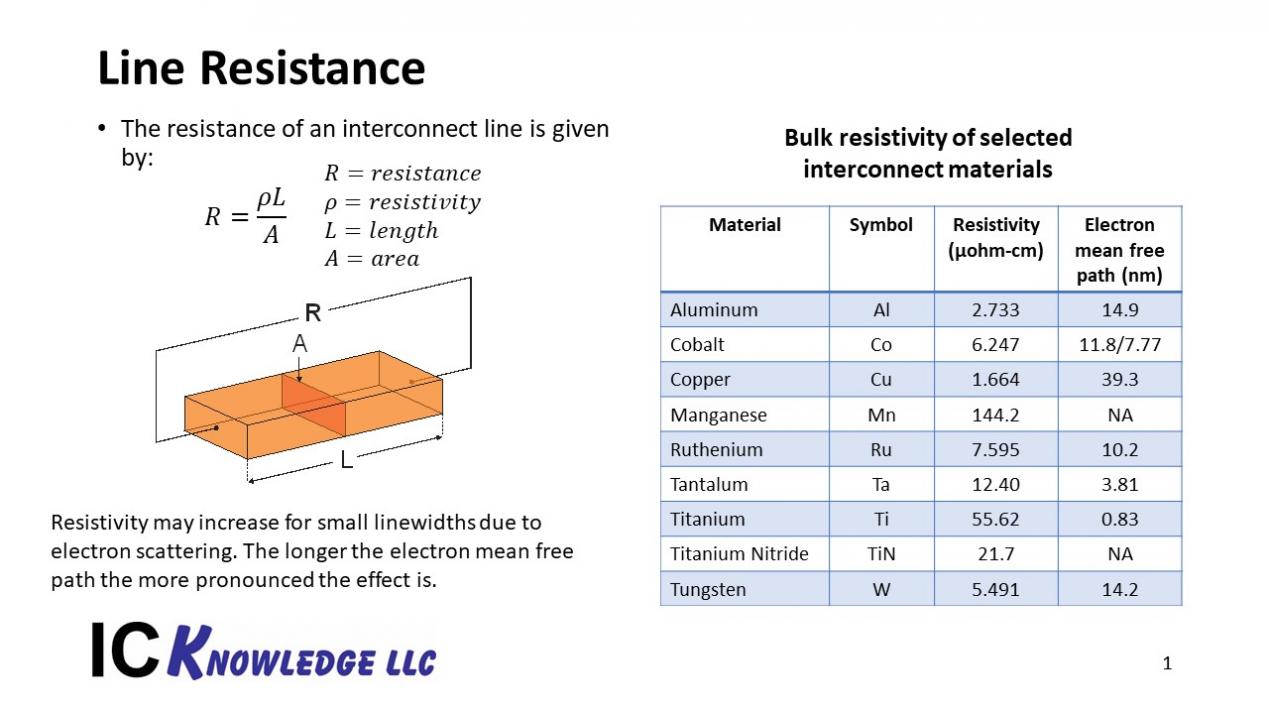

IITC – Imec Presents Copper, Cobalt and Ruthenium Interconnect Results

The IEEE Interconnect Technology Conference (IITC): Advanced Metallization Conference was held June 4th through 7th in Santa Clara. Imec presented multiple papers on comparing copper, cobalt and ruthenium interconnect. One paper in particular caught my eye: Marleen H. van der Veen, # N. Heylen, O. Varela Pedreira, S. Decoster,… Read More

7nm Networking Platform Delivers Data Center ASICs

We all know IP is critical for advanced ASIC design. Well-designed and carefully tested IP blocks and subsystems are the lifeblood of any advanced chip project. Those IP suppliers who can measure up to the need, especially at advanced process nodes, will do well, absolutely.

It is interesting to note that eSilicon now has a very … Read More

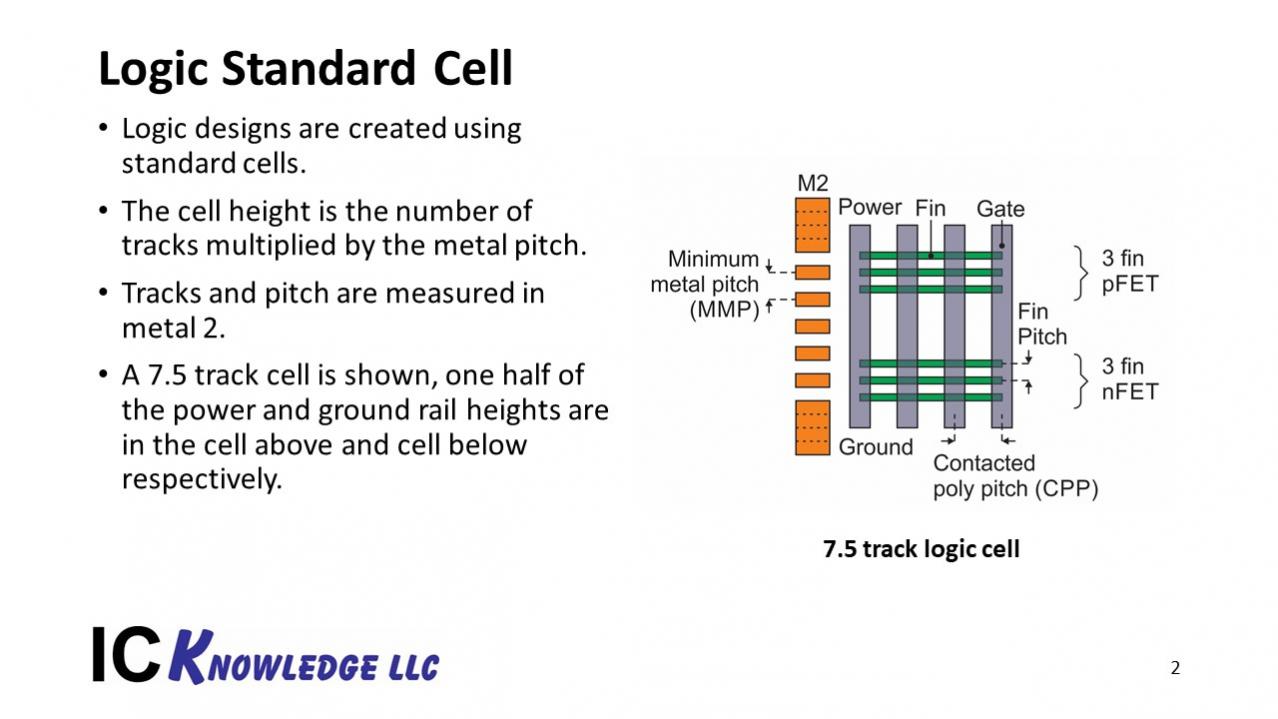

7nm, 5nm and 3nm Logic, current and projected processes

There has been a lot of new information available about the leading-edge logic processes lately. Papers from IEDM in December 2017, VLSIT this month, the TSMC and Samsung Foundry forums, etc. have all filled in a lot of information. In this article I will summarize what is currently known.… Read More

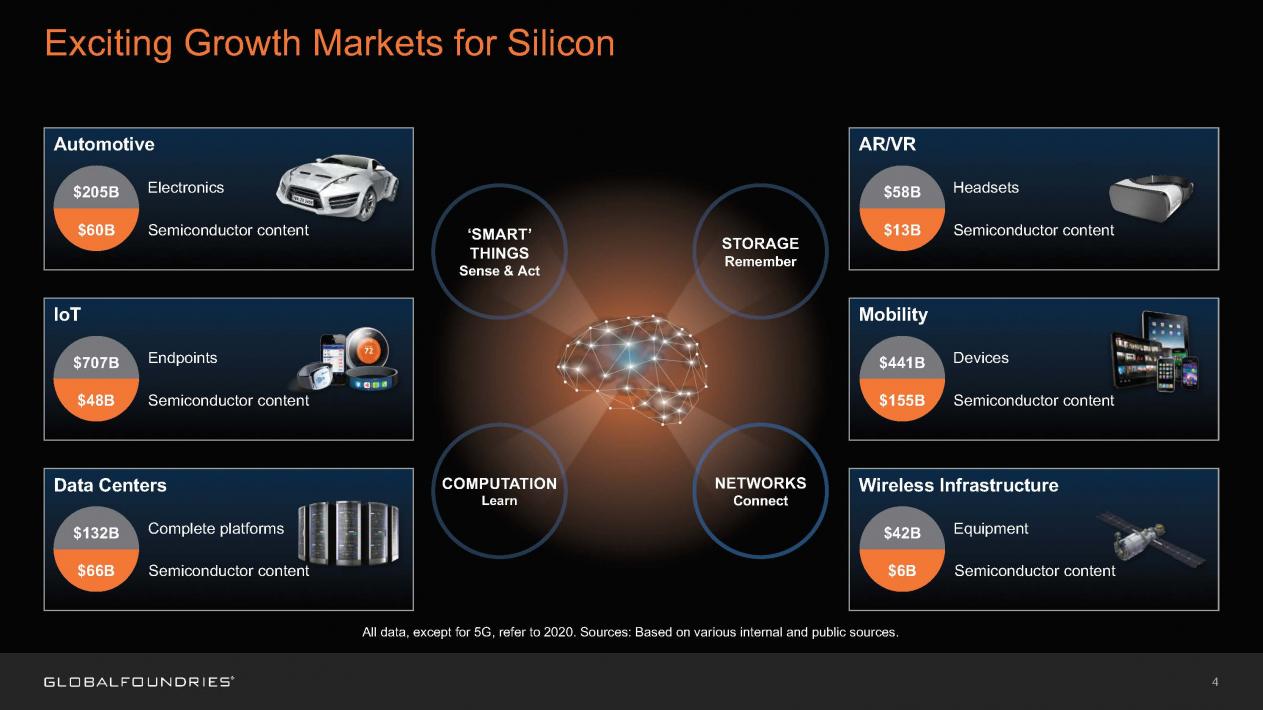

Imec Technology Forum: Gary Patton of GLOBALFOUNDRIES

The imec technology forum was held in Belgium last week. At the forum I had a chance to sit down with Gary Patton the CTO of GLOBALFOUNDRIES (GF) for an interview and he also presented “Enabling Connected Intelligence – Technology innovation: Enablers for an intelligent future” at the forum. In this article … Read More

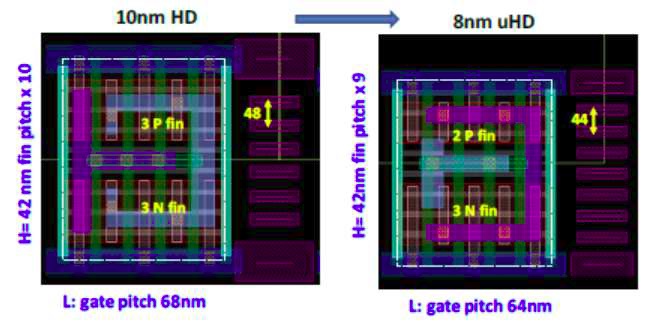

Samsung 10nm 8nm and 7nm at VLSIT

I got a tip sheet today for the upcoming 2018 Symposia on VLSI Technology & Circuits to be held June 19th through 21st in Honolulu, Hawaii. There is some interesting information on Samsung’s 10nm, 8nm and 7nm processes in the tip sheet:… Read More

Intel 10nm Yield Issues

On their first quarter earnings call Intel announced that volume production of 10nm has been moved from the second half of 2018 to 2019 due to yield issues. Specifically, they are shipping 10nm in low volume now, but yield improvement has been slower than anticipated. They report that they understand the yield issues but that improvements… Read More