You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Samsung and TSMC have both made recent disclosures about their 5nm process and I though it would be a good time to look at what we know about them and compare the two processes.

A lot of what has been announced about 5nm is in comparison to 7nm so we will first review 7nm.

7nm

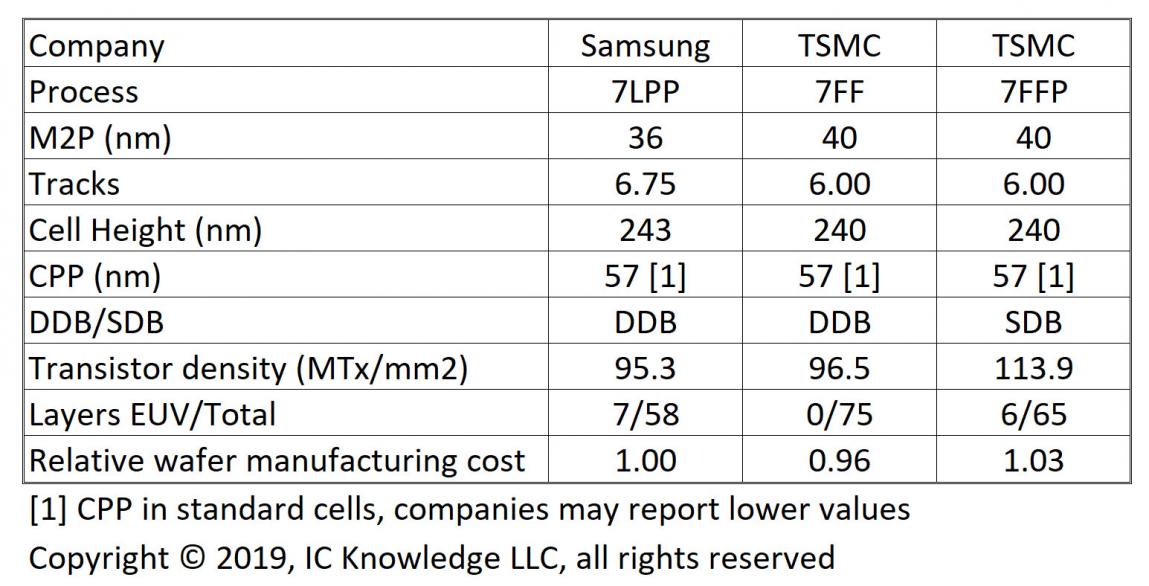

Figure 1 compares Samsung’s 7LPP process to TSMC’s 7FF and 7FFP… Read More

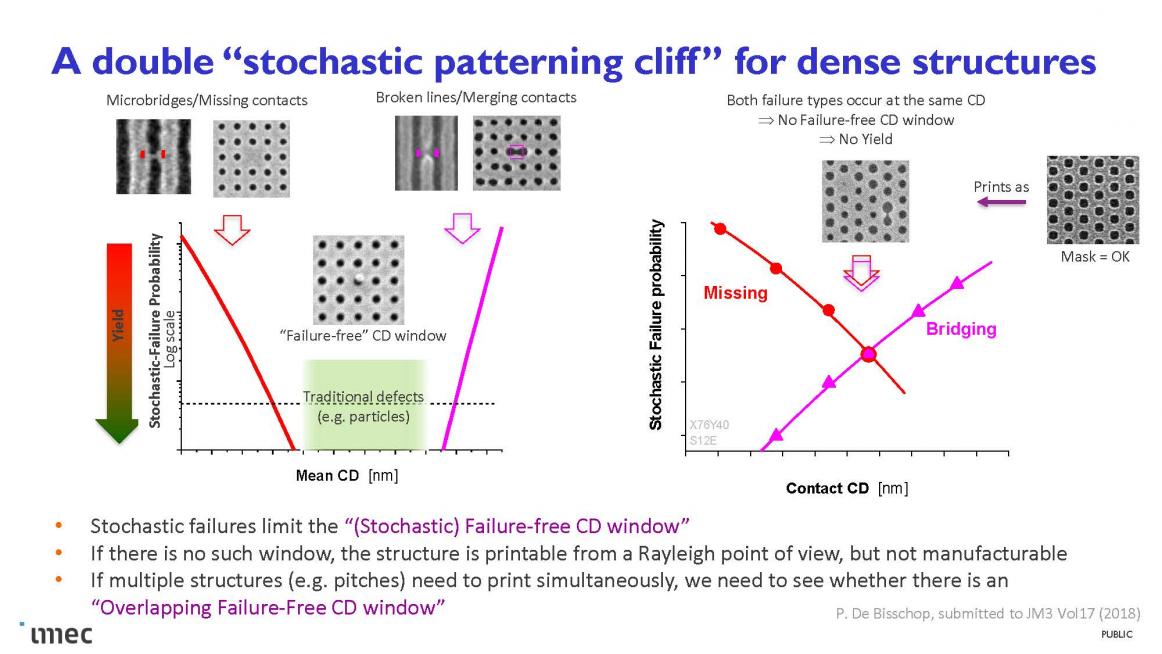

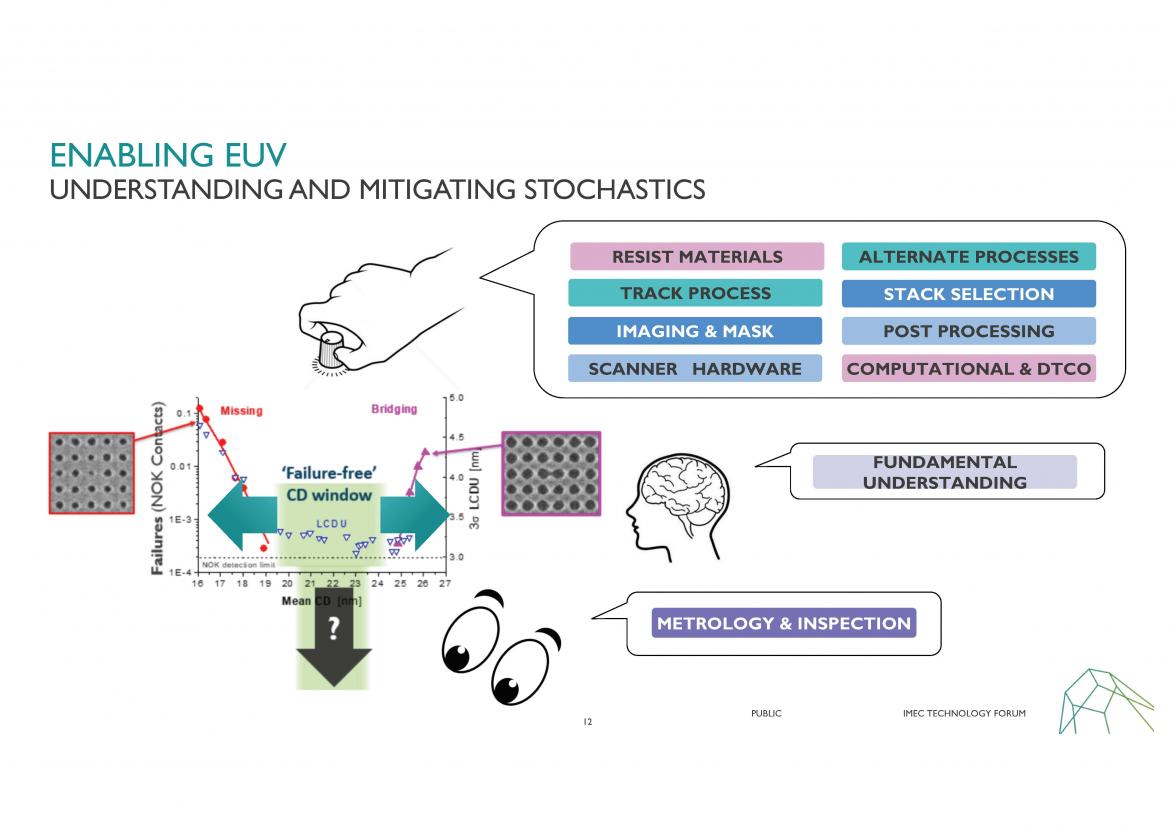

At the SPIE Advanced Lithography Conference Imec presented several papers on EUV and Veeco presented about etching for EUV masks. I had the opportunity to see the presentations and speak with some of the authors. In this article I will summarize the key issues around EUV based on this research.

EUV is ramping up into high volume 7nm… Read More

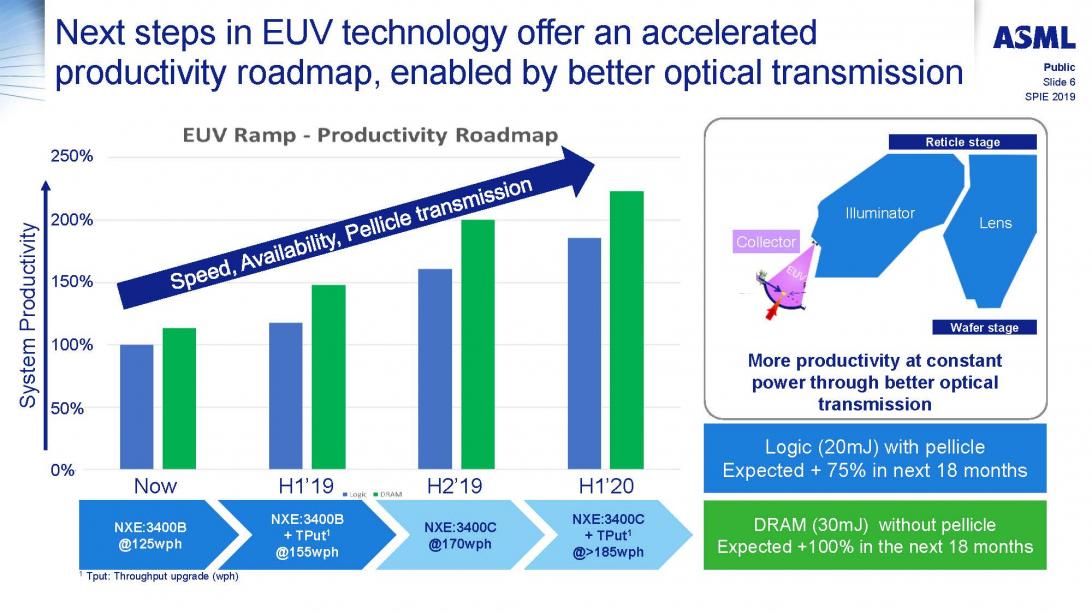

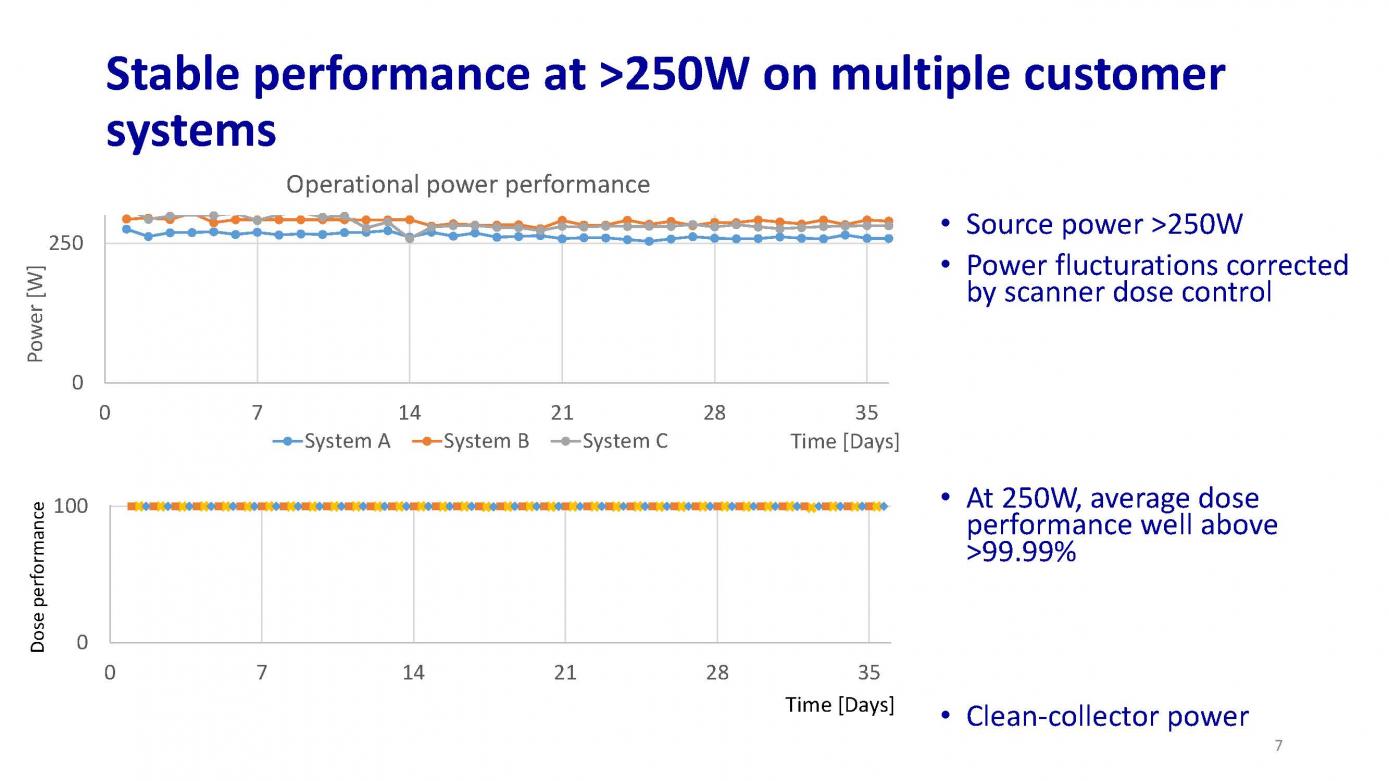

At the SPIE Advanced Lithography Conference ASML gave an update on both the current 0.33NA system and the 0.55 high-NA system development. I saw the presentations and got to sit down with Mike Lercel (Director of Strategic Marketing).… Read More

Last week I attended the 2019 SPIE Advanced Lithography Conference. I gave two presentations, attended dozens of papers and conducted three interviews. I will be doing some detailed write ups particularly on EUV but I am waiting for the presentations from several of the papers. In the mean time I thought I would put some overall … Read More

I was asked to present at Nikon’s LithoVision event again this year. LithoVision is held the day before the SPIE Advanced Lithography Conference also in San Jose. The following is a write up of my talk.… Read More

At IEDM last week Anthony (Tony) Yen, Vice President and Head, Technology Development Centers Worldwide for ASML presented a paper entitled “EUV Lithography at Threshold of High-Volume Manufacturing” authored by Anthony Yen, Hans Meiling, and Jos Benschop. At IEDM I had a chance to sit down with Tony and discuss the paper and … Read More

At SEMICON West I attended the imec technology forum, multiple Tech Spot presentations and conducted a number of interviews relevant to advanced lithography and EUV. In this article I will summarize what I learned plus make some comments on the outlook for EUV.… Read More

A Phase-Locked Loop (PLL) gives design a heartbeat. Despite its minute footprint, it has many purposes such as being part of the clock generation circuits, on-chip digital temperature sensor, process control monitoring in the scribe-line or as baseline circuitry to facilitate an effective measurement of the design’s power… Read More

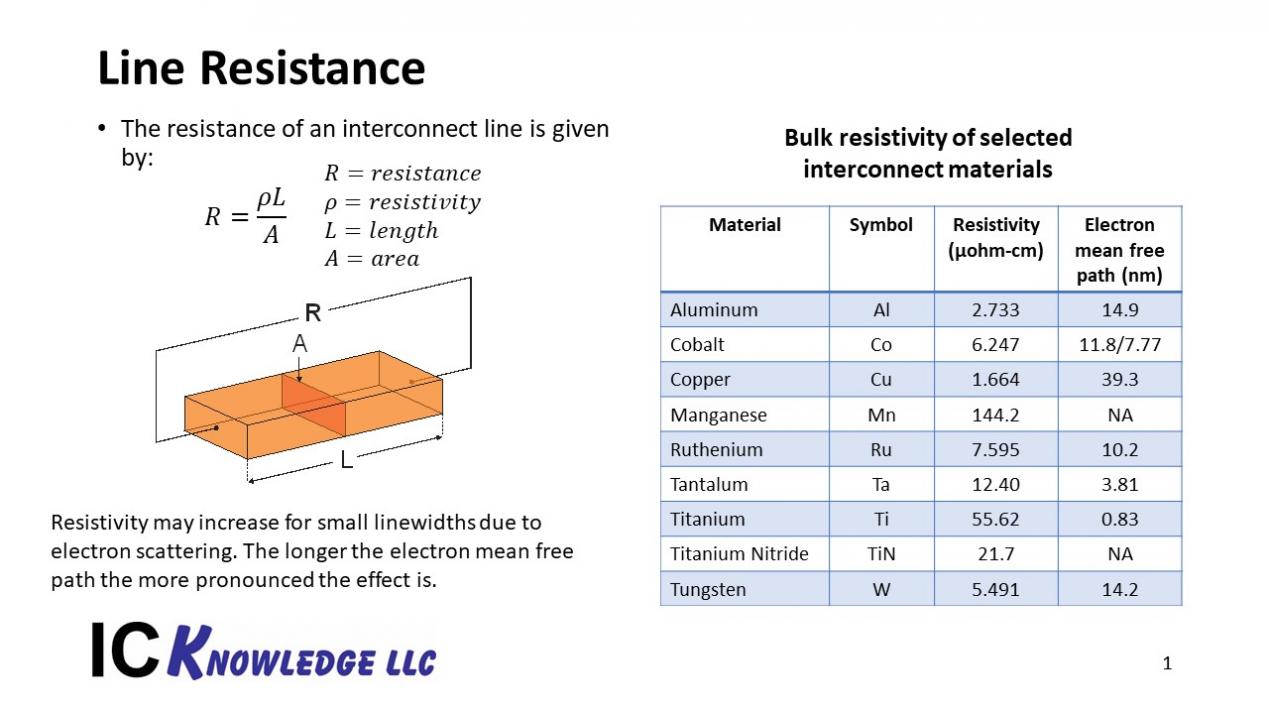

The IEEE Interconnect Technology Conference (IITC): Advanced Metallization Conference was held June 4th through 7th in Santa Clara. Imec presented multiple papers on comparing copper, cobalt and ruthenium interconnect. One paper in particular caught my eye: Marleen H. van der Veen, # N. Heylen, O. Varela Pedreira, S. Decoster,… Read More

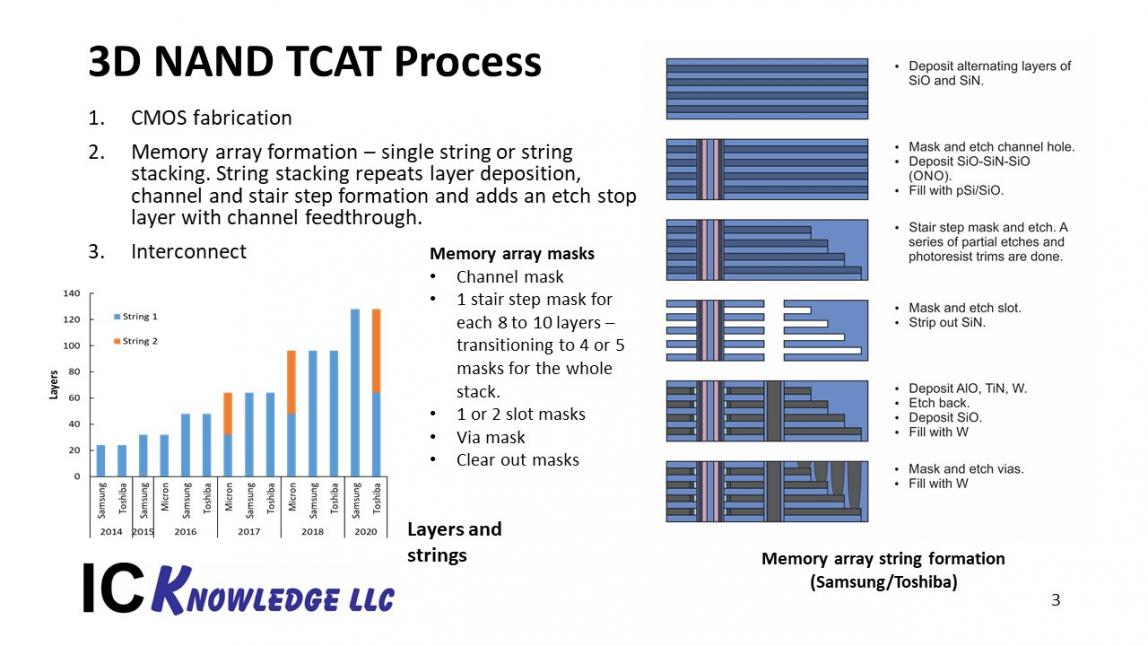

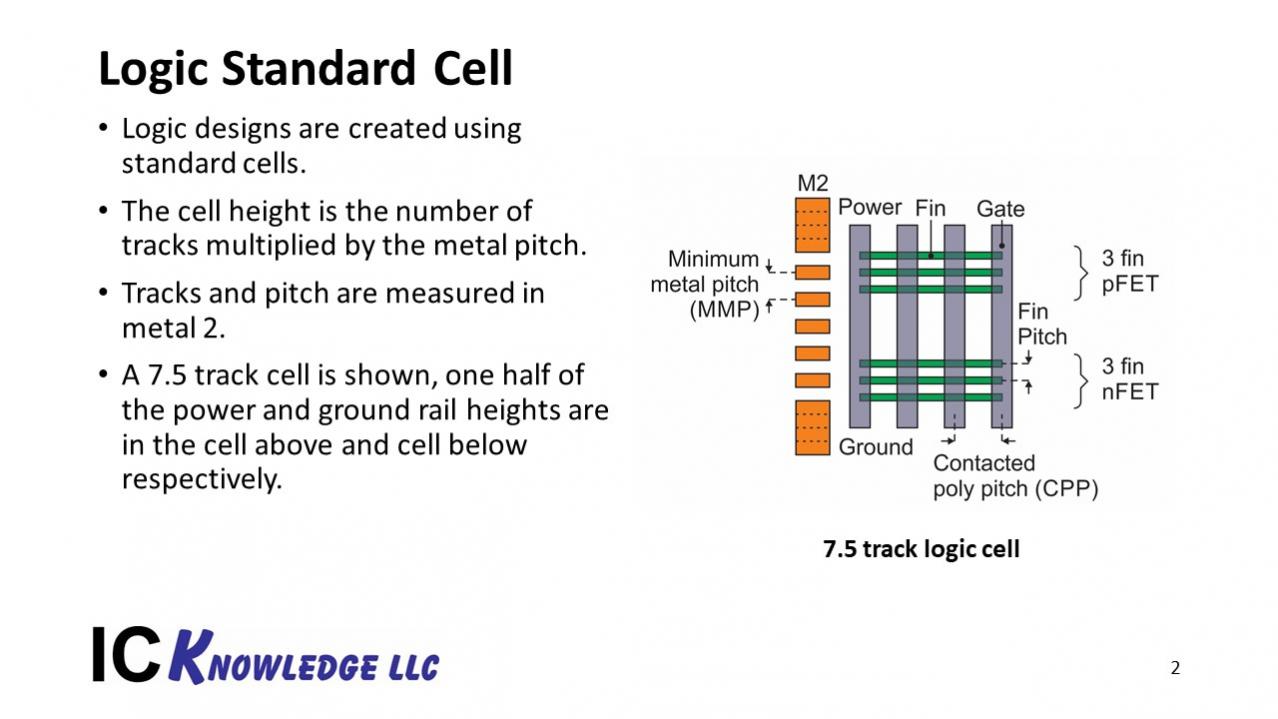

There has been a lot of new information available about the leading-edge logic processes lately. Papers from IEDM in December 2017, VLSIT this month, the TSMC and Samsung Foundry forums, etc. have all filled in a lot of information. In this article I will summarize what is currently known.… Read More