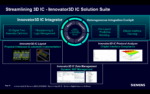

In a major announcement at the 2025 Design Automation Conference (DAC), Siemens EDA introduced a significant expansion to its electronic design automation (EDA) portfolio, aimed at transforming how engineers design, validate, and manage the complexity of next-generation three-dimensional integrated circuits (3D ICs).… Read More

Tag: 3d packaging

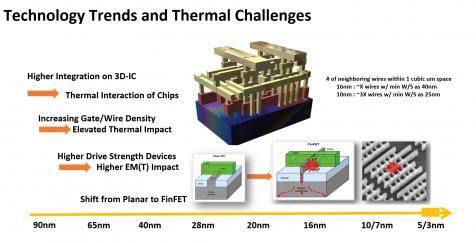

Advances in Physical Verification and Thermal Modeling of 3DICs

If, like me, you’ve been paying too little attention to historically less glamorous areas of chip design like packaging, you’ll wake up one day and realize just how much things have changed and continue to advance and how interesting it’s become.

One of the main drivers here is the increasing use of chiplets to counter the decreasing… Read More

EDA Flows for 3D Die Integration

Background

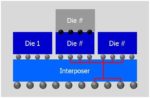

The emergence of 2.5D heterogeneous die integration using a silicon (or organic) interposer has enabled unique system architectures. The term “More than Moore” has been used to describe the circuit density and cost advantages of leveraging multiple die in the package, the die potentially in different process technologies. … Read More

Online Class: Advanced CMOS Technology 2020 (The 10/7/5 NM Nodes)

Our friends at Threshold Systems have a new ONLINE class that may be of interest to you. It’s an updated version of the Advanced CMOS Technology class held last February. This is normally a classroom affair but to accommodate the recent COVID-19 travel restrictions it is being offered virtually.

As part of the previous class we did… Read More

TSMC – Solid Q3 Beat Guide- 5G Driver – Big Capex Bump – Flawless Execution

TSMC puts up solid QTR, Capex increase for 5NM and capacity increase, 5G/mobile remains driver- HPC good 7NM, 27% of revs- Very nice margins!

In line quarter-Good guide

TSMC reported revenues of $9.4B and EPS of $0.62 , more or less in line with expectations, perhaps a touch below ” whisper” expectations which had been… Read More

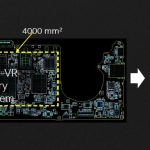

The Coming Tsunami in Multi-chip Packaging

The pace of Moore’s Law scaling for monolithic integrated circuit density has abated, due to a combination of fundamental technical challenges and financial considerations. Yet, from an architectural perspective, the diversity in end product requirements continues to grow. New heterogeneous processing units are being… Read More

ANSYS at DAC

I’m not going to be at DAC this year because I scheduled a fishing trip at the end of June, assuming the show would stay true to form as an early/mid-June event. Still, having to endure salmon and halibut fishing in Alaska rather than slogging around Moscone Center, I can’t pretend to be too disappointed; I’ll be thinking of you all 😎.… Read More

Thermal and Reliability in Automotive

Thermal considerations have always been a concern in electronic systems but to a large extent these could be relatively well partitioned from other concerns. Within a die you analyze for mean and peak temperatures and mitigate with package heat-sinks, options to de-rate the clock, or a variety of other methods. At the system level… Read More

“Thinking Outside the Chip”

While pushing Moore’s Law’s boundaries in the world of 2D packaging, companies are starting to explore nontraditional approaches towards designing integrated circuit chips. 2D packaging is currently the most used method in designing chips in the industry, and while it leads in efficiency of power and performance, it lacks … Read More