You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Sidense is an interesting company in a very important market segment. Sidense was founded in 2004 and their 1T-OTP memory macros are now used in hundreds of chips from 180nm to 16nm for code storage, secure encryption keys, analog and sensor trimming and calibration, ID tags, and chip and processor configuration.

If you are designing… Read More

The cost trend for leading edge semiconductor technologies is a subject of some controversy in the industry. Cost is a complex issue with many interacting factors and much of the information out in the industry is in my opinion misleading or incorrect. In this article, I will discuss each of the factors as well as present a view of … Read More

Standard cell and memory IP are key enablers for new process node availability. These two items must be in place early and be completely ready for a process node to scale to volume. Development of both leaves no room for error and they require the highest performance possible. Foundries are extremely focused on this and spend a lot… Read More

The leading edge semiconductor logic landscape has in recent years collapsed to just four companies. The following is a summary of what is currently known about each company’s plans and how they compare. ASML has analyzed many logic nodes and developed a formula that normalizes processes to a “standard node”.… Read More

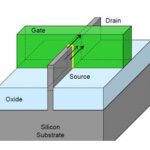

Sofics recently had the opportunity to characterize FinFET technology through cooperation with one of its customers. We analyzed the technology related to ESD and identified several challenges.… Read More

Being that TSMC and Solido are founding members of SemiWiki, you should be able find out everything you ever wanted to know on their respective landing pages. If not, just ask a question in the SemiWiki forum and I can assure you it will be answered in great detail. And here are some other interesting 2015 factoids from Solido:… Read More

I have written multiple articles about this year’s SPIE Advanced Lithography Conference describing all of the progress EUV has made in the last year. Source power is improving, photoresists are getting faster, prototype pellicles are in testing, multiple sites around the world are exposing wafers by the thousands and more. … Read More

At ISSCC this year Samsung published a paper entitled “A 10nm FinFET 128Mb SRAM with Assist Adjustment System for Power, Performance, and Area Optimization. In the paper Samsung disclosed a high density 6T SRAM cell size of 0.040µm[SUP]2[/SUP]. I thought it would be interesting to take a look at how this cell size stacks … Read More

About 35 years ago the first commercial SPICE circuit simulators emerged and they were quickly put to work helping circuit designers predict the timing and power of 6um NMOS designs. Then we had to limit our circuit simulations to just hundreds of transistors and interconnect elements to fit into the RAM and complete simulation… Read More

It used to be that GPU chips moved to new process nodes pretty frequently, previously as often as annually. That is up until 2011. That was the year that 28nm GPU’s were unveiled. Since then there has been a long pause. Now in the wake of the 2016 CES both Nvidia, with its previously announced Pascal, and AMD, with the just announced Polaris,… Read More