You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

At the ISS conference held from April 4th through 6th I presented on who I thought would have the leading logic technology in 2025. The following is a write up of that presentation.

ISS was a virtual conference in 2021 and I presented on who currently had logic leadership and declared TSMC the clear leader. Following that conference,… Read More

I was asked to give a talk at the 2021 ISS conference and the following is a write up of the talk.

The title of the talk is “Logic Leadership in the PPAC era”.

The talk is broken up into three main sections:

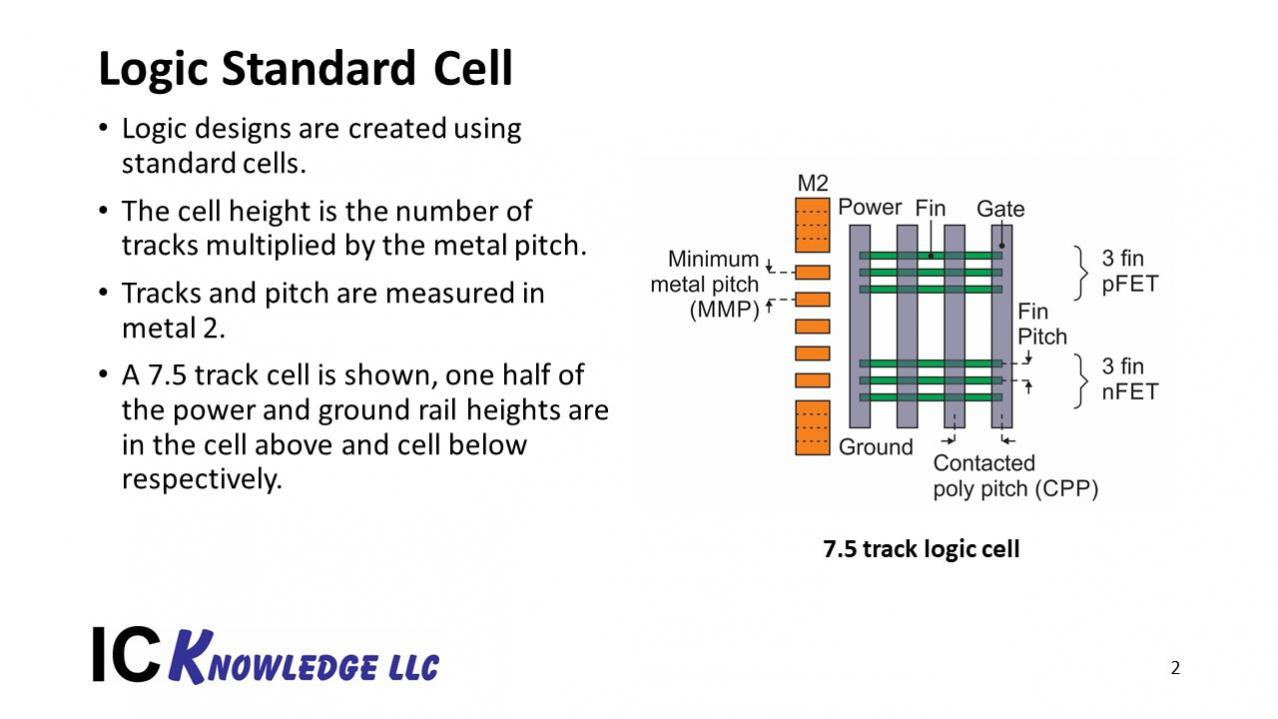

- Background information explaining PPAC and Standard Cells.

- A node-by-node comparisons of companies running leading edge logic

…

Read More

Seeking Alpha just published an article about Intel and Samsung passing TSMC for process leadership. The Intel part seems to be a theme with them, they have talked in the past about how Intel does bigger density improvements with each generation than the foundries but forget that the foundries are doing 5 nodes in the time it takes… Read More

I have seen several articles recently discussing foundry wafer selling prices for leading edge wafers, these articles all quote estimates from a paper by the Center for Security and Emerging Technology (CSET). The paper is available here.

My company IC Knowledge LLC is the world leader in cost and price modeling of semiconductors… Read More

Automotive applications are having a tremendous influence on semiconductor design. This influence is coming from innovations in cloud computing, artificial intelligence, communications, sensors that all serve the requirements of the automotive market. It should come as no surprise that ADAS and autonomous driving are … Read More

The most viewed blogs I write for SemiWiki are consistently blogs comparing the four leading edge logic producers, GLOBALFOUNDRIES (GF), Intel, Samsung (SS) and TSMC. Since the last time I compared the leading edge new data has become available and several new processes have been introduced. In this blog I will update the current… Read More

I have previously published analysis’ converting leading edge logic processes to “standard nodes” and comparing standard nodes by company and time. Recently updated details on the 7nm process node have become available and in this article, I will revisit the standard node calculations and trends.… Read More

The first transistor was made of two electrodes, held in place by plastic, making contact with a piece of doped germanium. Ever since then, devices and their packaging have been performing a complicated and oftentimes intricate dance. Single transistor devices became integrated circuits, and along the way separate IC’s were… Read More

Last week Intel held a manufacturing day where they revealed a lot of information about their 10nm process for the first time and information on competitor processes continues to slowly come out as well. I thought it would be useful to summarize what we know now, especially since some of what Intel announced was different than what… Read More

I was invited to give a talk at this year’s ISS conference, the talk seemed to be very well received and I was asked to blog about it for SemiWiki. Parts of the talk will be familiar to SemiWiki readers from some of my previous blogs but I also went into more detail around some scaling challenges. The following is a summary of what… Read More