At TSMC’s OIP Symposium recently, Xilinx announced that they would not be building products at the 10nm node. I say “announced” since I was hearing it for the first time, but maybe I just missed it before. Xilinx would go straight from the 16FF+ arrays that they have announced but not started shipping, and to the… Read More

Tag: 16nm

SEMI SMC: Atoms Still Don’t Scale

Last Tuesday was the SEMI’s annual Strategic Materials Conference (SMC). The opening keynotes were given by Gary Patton, the CTO of GlobalFoundries, and Mark Thirsk, Managing Partner of Linx Consulting. This year it was held in the Computer History Museum (which always makes the commute interesting since you have to fight… Read More

TSMC OIP: What to Do With 20,000 Wafers Per Day

Today it is TSMC’s OIP Ecosystem Innovation forum. This is an annual event but is also a semi-annual update on TSMC’s processes, investment, volume ramps and more. TSMC have changed the rules for the conference this year: they have published all the presentations by their partners/customers. Tom Quan of TSMC told… Read More

Tackling Layout Gradient Effects in 16 nm FinFET using Layout Automation

My first exposure to automating IC layout was back in the 1980’s at Intel where I coded a layout compiler to auto-generate about 6% of a graphics processor chip. The need to use automation for IC layout continues today, and with the advent of FinFET technology there are some new challenges like layout gradient effects that … Read More

Xilinx Datacenter on a Chip

I talked recently about the Intel acquisition of Altera which seems to be all about using FPGA technology to build custom accelerators for the datacenter. Some algorithms, especially in search, vision, video and so on map much better onto a hardware fabric than being implemented in code on a regular microprocessor.

So if the heart… Read More

Synopsy Eats Their Own Dogfood

One of the most interesting presentations that I went to was the last presentation at the Synopsys Custom Lunch (no, the lunch wasn’t custom, we all got the same, but the presentations were about custom design). Since the last presentation was by Synopsys themselves and not by a customer, it wouldn’t seem promising that it could … Read More

Heard on the Street at ITF

As I said yesterday, I’m at the imec Technology Forum (ITF) in Brussels. So what have I learned from all the people that I’ve interacted with.

There were two press releases announced at a press conference yesterday. The first was that imec was expanding its relationship with Toshiba and Sandisk. This covers bringing… Read More

A Key Partner in the Semiconductor Ecosystem

Often we hear about isolated instances of excellence from various companies in the semiconductor industry which contribute significantly in building the overall ecosystem. While the individual excellence is essential, it’s rather more important how that excellence is utilized in a larger way by the industry to create a ‘value… Read More

Antifuse is the New Foundation of NVM Below 16nm

Today the non-volatile memory (NVM) foundation is the eFuse. It is typically available for free from the foundry and is the default choice because, like Mount Everest, it is there. However, like Mount Everest it is big. It is also power hungry and slow. eFuse solutions blow the silicide on the poly line creating a change in resistance.… Read More

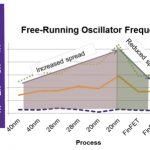

Moore’s Law is dead, long live Moore’s Law – part 4

In the third installment of this series we discussed the status of DRAM scaling and Moore’s law. In this installment we will tackle logic. The focus will be on foundry logic.

Logic technology challenges

In the second installment of this series we discussed constant electric field scaling. As we mentioned in that installment at … Read More