Sondrel just released a position paper on how to model and design a complex ASIC. We have been following Sondrel for the past year and I have found their collateral to be excellent. Here is the position paper overview, a description of the new Sondrel modeling tool, the 10 steps, and of course a link to download the paper:

Overview

It is important to model an SoC well in advance to avoid costly over design or insufficient performance and to create a hardware emulate on which representative end user applications can be run. Detailed architectural modelling provides reasonable estimates of the performance, power, memory resources, and the NoC (Network on Chip) configuration that will be required along with an indicative size of the die and what it is likely to cost. With this information, a customer can decide whether to proceed with the design, if it needs to be adjusted or even cancelled. Sondrel™ has created unique, proprietary modelling flow software, initially for use with Arm® and Synopsys® tools, that dramatically reduces the time to do this from months to a few days, which Sondrel claims to be an industry first for a services organisation. This article discusses how modelling is used in the ten steps of modelling and designing a complex SoC architecture.

Sondrel’s new tool

Modelling tools are available as standard items from leading vendors but what Sondrel does is to wrap the vendor’s offerings with its own custom flow. The vendor’s tools are limited in terms of automation and ways that they can be adjusted but Sondrel’s new modelling flow tool adds a framework with a much greater number of settings that can be tweaked by the Sondrel Systems Architect who is working on the project. This is added using hooks into the vendor’s software that are provided for this very purpose. Typically, users create customisation wrappers that are specific to the designs that they work on if not already present in a library of an ever-growing number of such wrappers. However, because Sondrel works on a wide variety of projects for a plethora of customers, it has defined a methodology and flows that are unique and broader in scope so that they can be used for almost any architectural exploration project.

The biggest benefit of the modelling flow’s dramatic reduction in the time it takes to create a model and run simulations, is that Sondrel can provide customers with data on the likely performance of a proposed ASIC in a matter of few days to determine if the architecture proposed gives an appropriate set of numbers. If not, it is very easy and quick to run variants of the model simply by changing the settings of the existing model to decide which is the best one for the customer’s application use case. Running each variation takes anywhere between a few minutes to an hour, so the whole process of model creation and running variants can still be done in a few days.

For comparison, converging on a candidate architecture without Sondrel’s modelling flow tool would rely heavily on static spreadsheet modelling which would take several weeks and then each variant of the model to evaluate different architectures would each take weeks as each variant model would have to be created from scratch. Overall, that could total a number of months.

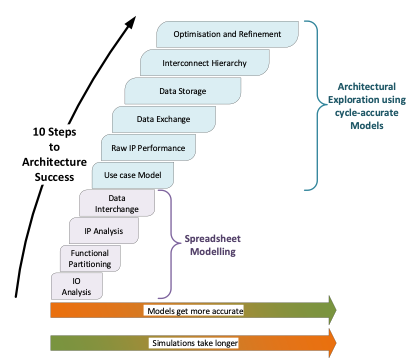

The 10 steps are: –

- Determines what the data is and what are the I/O constraints such as burstiness, latency, timing, and data formatting, to decide on the buffer requirements that is captured in a spreadsheet.

- Breaks the processing down into sub-tasks and groups parts of the SoC into common pieces of functionality.

- Identifies what third party IP blocks will be required to perform the steps of an algorithm and how much memory and compute power they require from their datasheets that can be fed into the modelling environment to give a more accurate representation of what all the IP blocks will be doing.

- Covers the method of exchanging data in between parts of an algorithm such as on-chip SRAM or external DDR memory as well as FIFO which are small spaces of memory on chip. The decision between SRAM and DDR depends on the size of the data and how often it needs to be accessed with large pieces of data going to external memory and small pieces of data to SRAM or FIFO.

- This is when a software representation is created of what the different stages are with the conceptual view of the algorithm and actual simulation objects that correspond to the different software stages of the algorithm. These require settings such as latency and processing cycles, and are joined by objects known as channels that indicate what the sequencing is.

- Having constructed all the simulation objects for the full algorithm, simulations can be run to see if the right sequencing of the algorithm has been captured.

- Uses models of the hardware platform with VPUs (Virtual Processor Units) that will run the software of step 5, each with its own local memory. Here the interface timing can be considered and communication domains defined with their assigned channels and evaluated. It also enables the configuration of the VPUs to be verified as correct.

- Takes the memory available to each VPU and remodels it as being connected to external memory via a common memory controller. This gives a more accurate representation of the connectivity of all the VPUs and memories in the final system.

- Adds the interconnect fabric. Instead of the direct connections between the VPUs and the memory controller, these are replaced by the interconnect fabric and the effects on the timing and performance evaluated. The interconnect fabric is then adjusted to meet the performance required, with previous stages being redone to achieve the required results.

- This is a good working model so, by simply adjusting settings, various simulations can be run to identify bottlenecks, what constraints there are in the system, and which parameters should be adjusted to improve the throughput and reduce the latency of the SoC. These take a few minutes to an hour to run so that it is straightforward and quick to test variants.

The first four steps can be done on paper or on a spreadsheet by calculation to understand the input/output dataflows into the SoC and what their characteristics are. The last six steps are simulation-based where software models are constructed and simulations run to generate results that inform about the system.

An article covering this in more depth is available by clicking here.

About Sondrel™

Founded in 2002, Sondrel is the trusted partner of choice for handling every stage of an IC’s creation. Its award-winning, define and design ASIC consulting capability is fully complemented by its turnkey services to transform designs into tested, volume-packaged silicon chips. This single point of contact for the entire supply chain process ensures low risk and faster times to market. Headquartered in the UK, Sondrel supports customers around the world via its offices in China, India, Morocco and North America. For more information, visit www.sondrel.com

Also read:

Build a Sophisticated Edge Processing ASIC FAST and EASY with Sondrel

Sondrel Creates a Unique Modelling Flow to Ensure Your ASIC Hits the Target

Get a Jump-Start on Your Next IoT Design with Sondrel’s SFA 100

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.