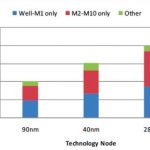

The semiconductor design and manufacturing challenges at 40nm and 28nm are a direct result ofMoore’s Law, the climbing transistor count and shrinking geometries. It’s a process AND design issue and the interaction is at the transistor level. Transistors may be shrinking, but atoms aren’t. So now it actually matters when even… Read More

The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More

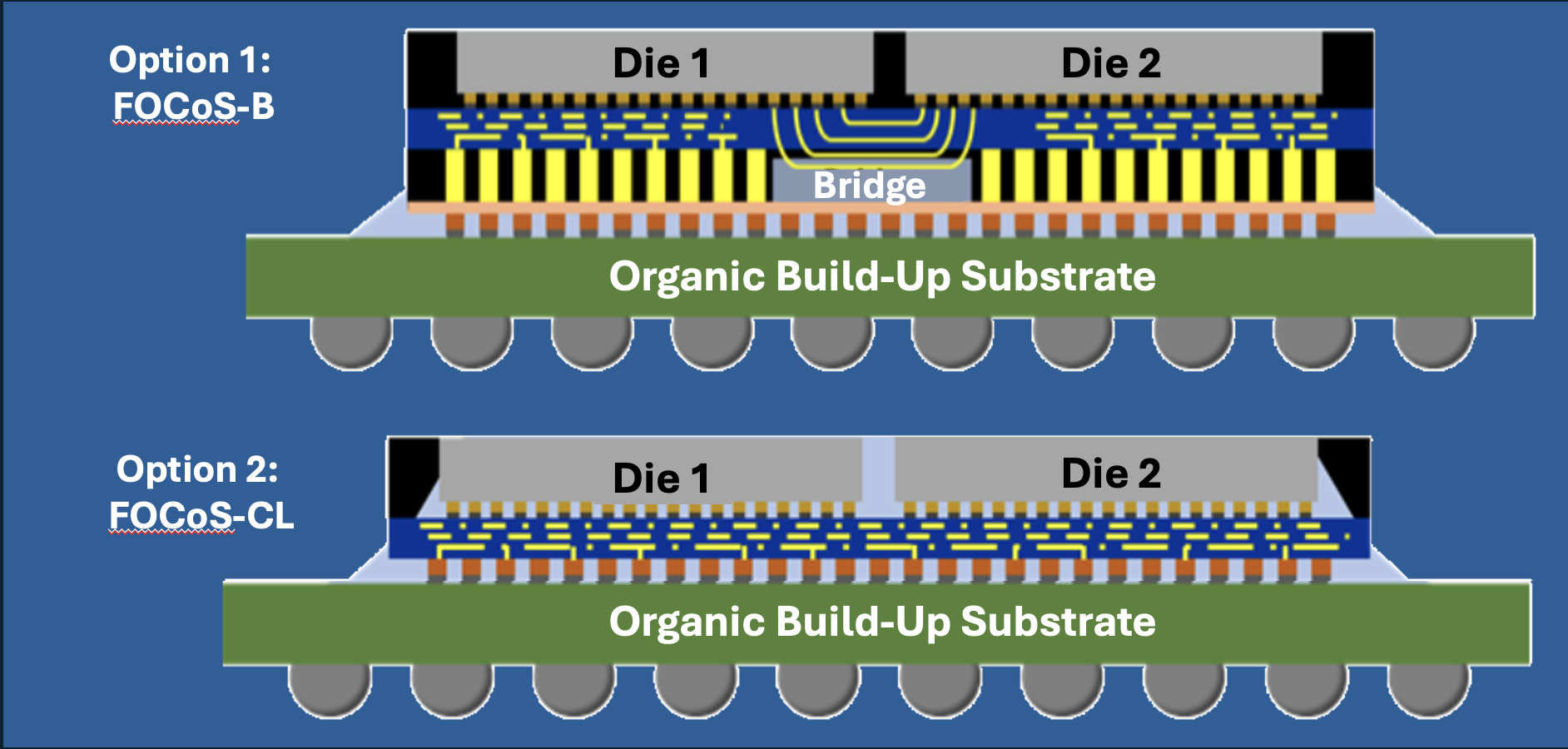

The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More

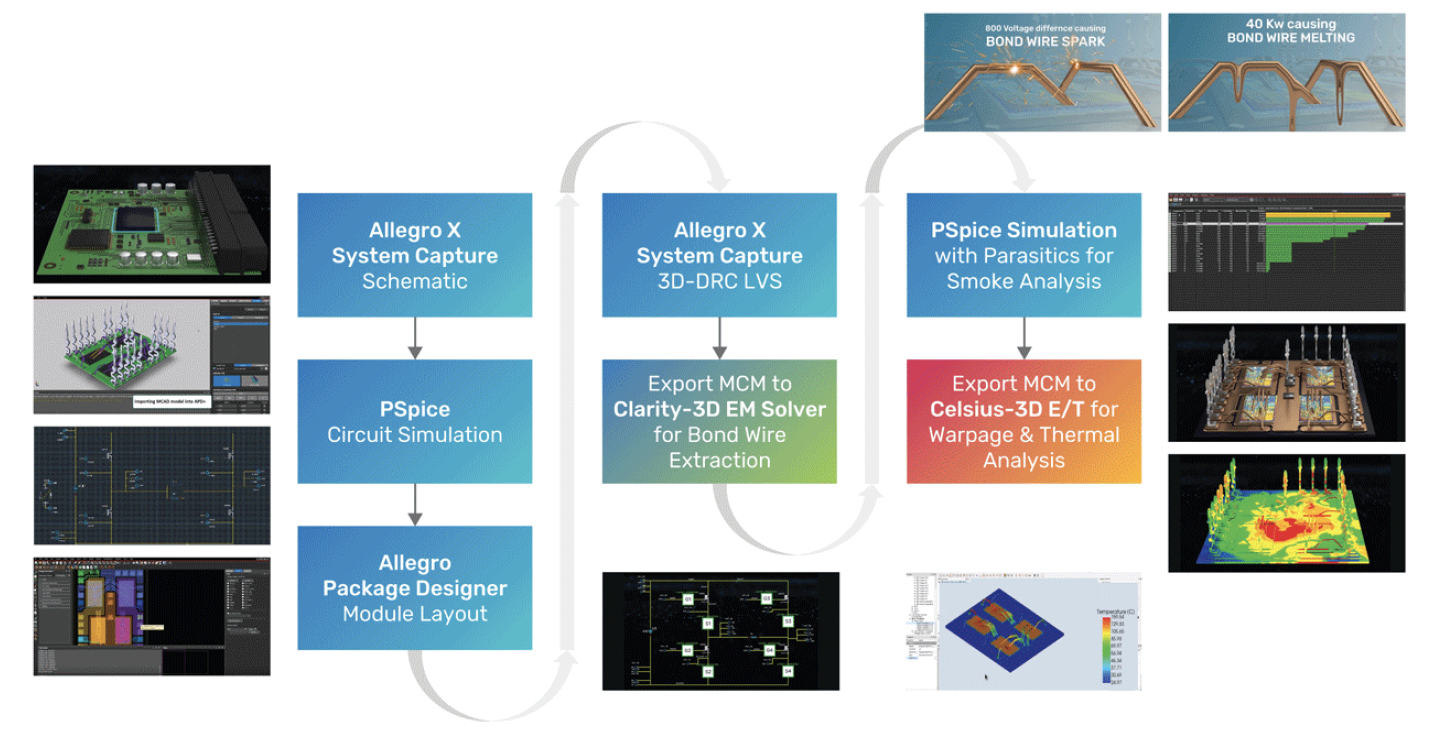

Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More Addressing Reliability and Safety of Power Modules for Electric VehiclesAs electric vehicles (EVs) gain widespread adoption, safety,…Read More

Addressing Reliability and Safety of Power Modules for Electric VehiclesAs electric vehicles (EVs) gain widespread adoption, safety,…Read More Shaping Tomorrow’s Semiconductor Technology IEDM 2024Anyone who has read my articles about IEDM…Read More

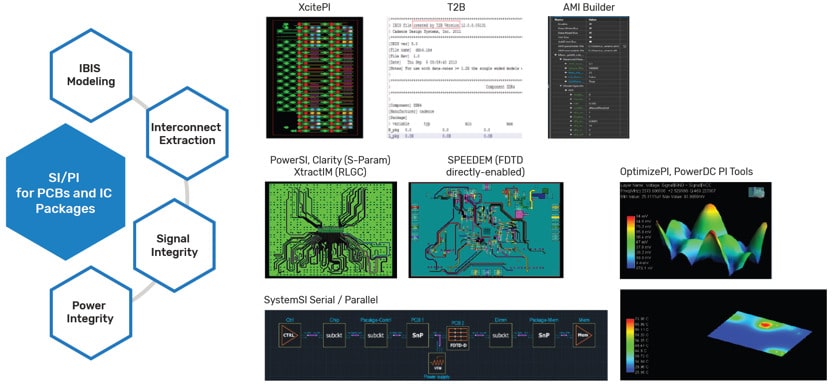

Shaping Tomorrow’s Semiconductor Technology IEDM 2024Anyone who has read my articles about IEDM…Read More SI and PI Update from Cadence on Sigrity XSignal Integrity (SI) and Power Integrity (PI) issues…Read More

SI and PI Update from Cadence on Sigrity XSignal Integrity (SI) and Power Integrity (PI) issues…Read MoreGetting Real Time Calibre DRC Results

Last week I met with Joseph Davis, Ph.D. at Mentor Graphics in Wilsonville, Oregon to learn about a new product designed for full-custom IC layout designers to improve productivity.

The traditional flow for full-custom IC layout designers has been nearly unchanged for decades:

- Read a schematic or use Schematic Driven Layout

Semiconductor IP would be nothing without VIP…

…but what is the weight of the Verification IP market?

If the IP market is a niche market (see: **) with revenue of about 1% of the overall semiconductor business, how could we qualify the VIP market? Ultra-niche market? But the verification of the IP integrated into the SoC is an essential piece of the engineering puzzle when you are… Read More

Apple Creates Semiconductor Opportunities . . .

There has been a lot of press this past week surrounding the release of iPad2. While it has some significant improvements, they are, for the most part, incremental. In my view the lack of flash, a USB port and a memory card slot continue to be huge deficits. Until this past week my reservations about the iPad have been mostly theoretical,… Read More

TSMC 2011 Technology Symposium Theme Explained

The 17[SUP]th[/SUP] Annual TSMC Technology Symposium will be held in San Jose California on April 5[SUP]th[/SUP], 2011. Dr. Morris Chang will again be the keynote speaker. The theme this year is “Trusted Technology and Capacity Provider”and I think it’s important to not only hear what people are saying but also understand why… Read More

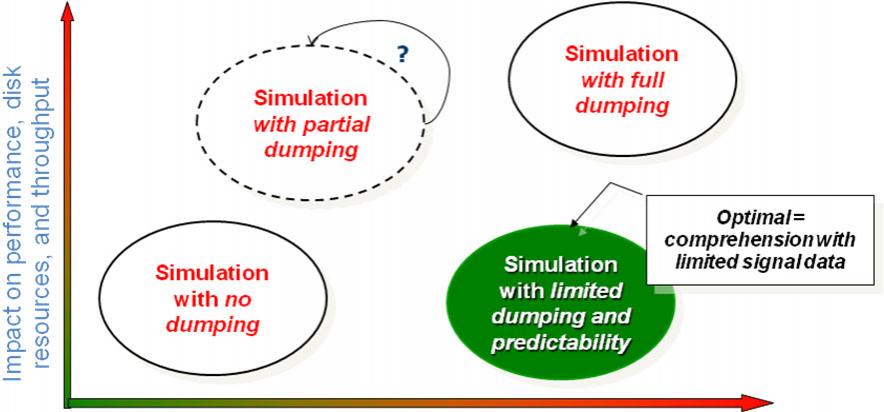

Essential signal data and Siloti

One of the challenges with verifying today’s large chips is deciding which signals to record during simulation so that you can work out the root cause when you detect something anomalous in the results. If you record too few signals, then you risk having to re-run the entire simulation when you omitted to record a signal that… Read More

Mentor Graphics 1 : Carl Icahn 0!

This is just another blog about Carl Icahn and his quest to conquer EDA, when in fact EDA is conquering him. It includes highlights from my dinner with Mentor Graphics and Physicist Brian Greene, the Mentor Q4 conference call, and meeting Mentor CEO Wally Rhines at DvCon 2011.

It wasn’t just the free food this time, dinner with Brian… Read More

Clock Domain Crossing, a potted history

Yesterday I talked to Shaker Sarwary, the senior product director for Atrenta’s clock-domain crossing (CDC) product SpyGlass-CDC. I asked him how it came about. The product was originally started nearly 8 years ago, around the time Atrenta itself got going. Shaker got involved about 5 years ago.

Originally this was a small… Read More

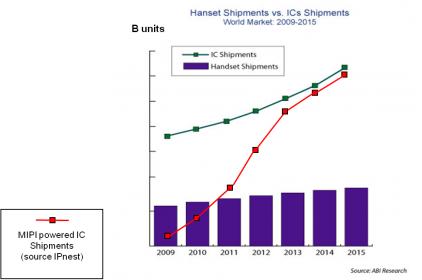

All you want to know about MIPI IP… don’t be shy, just ask IPnest

According with the MIPI Alliance, the year 2009 has been the time for MIPI specification to be developed, when 2010 was dedicated to Marketing and Communication effort to popularize MIPI technologies within the SC industry, finally the year 2011 is expected to see MIPI deployment in the mass market, at least in the Wireless (Handset)… Read More

Semiconductor Power Crisis and TSMC!

Power grids all over the world are already overloaded even without the slew of new electronic gadgets and cars coming out this year. At ISSCC, Dr. Jack Sun, TSMC Vice President of R&D and Chief Technology Officer made the comparison of a human brain to the closest thing available in silicon, a graphical processing unit (GPU).… Read More

AI Semiconductor Market