While Intel is doing victory laps in the race to a 3D transistor (FinFet) @ 22nm, TSMC is in production with 3D IC technology. A 3D IC is a chip in which two or more layers of active electronic components are integrated both vertically and horizontally into a single circuit. The question is which 3D race is more important to the semiconductor… Read More

Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V SolutionFounded with a vision to create transformative, customizable…Read More

Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V SolutionFounded with a vision to create transformative, customizable…Read More Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early AdoptersThe demand for high-performance computing (HPC), data centers,…Read More

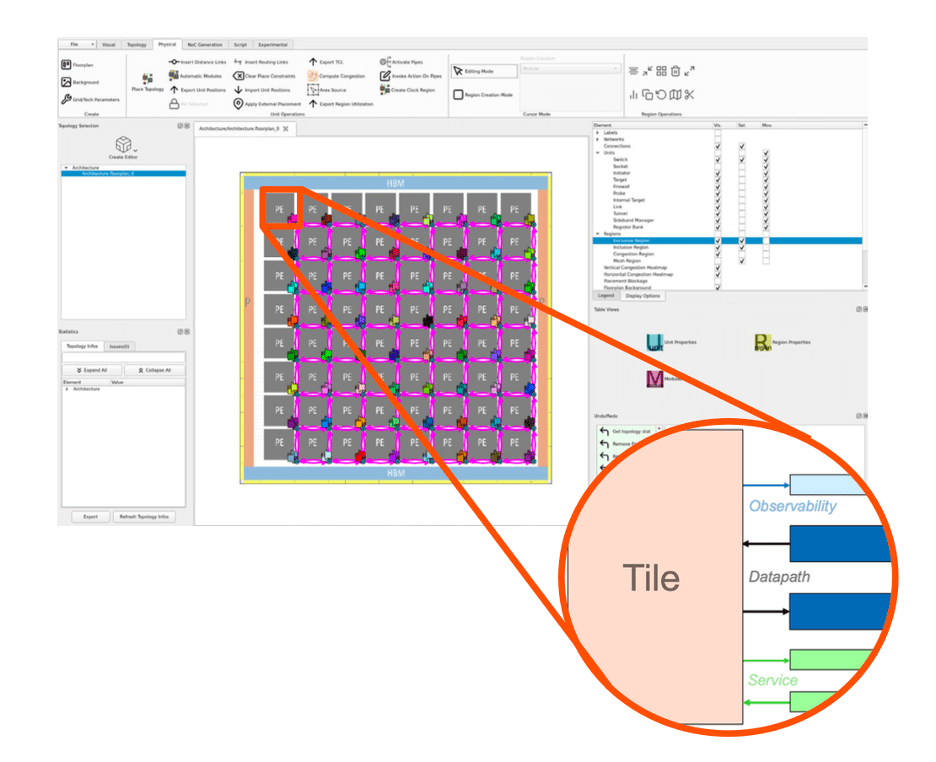

Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early AdoptersThe demand for high-performance computing (HPC), data centers,…Read More Arteris Empowering Advances in Inference AcceleratorsSystolic arrays, with their ability to highly parallelize…Read More

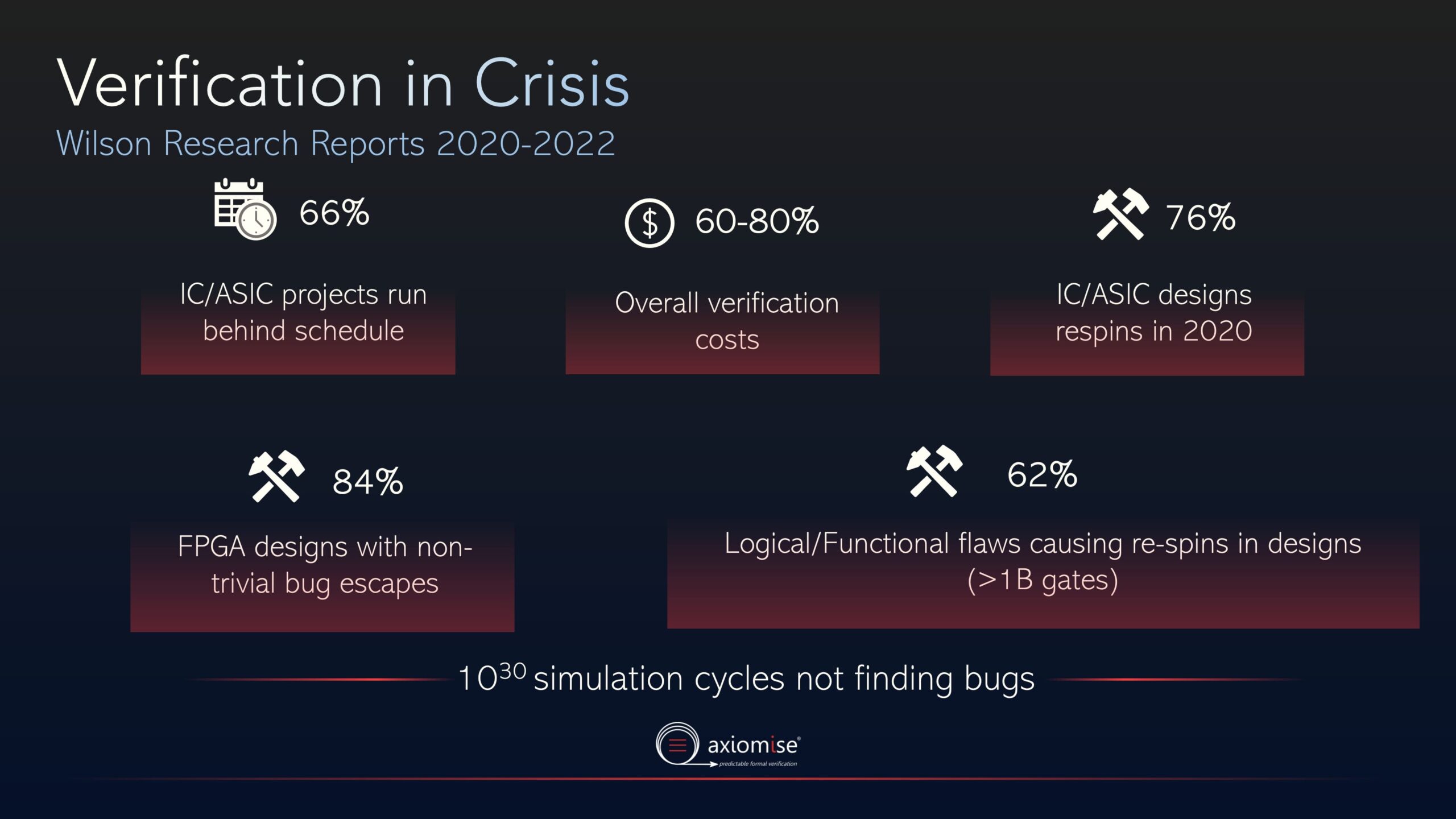

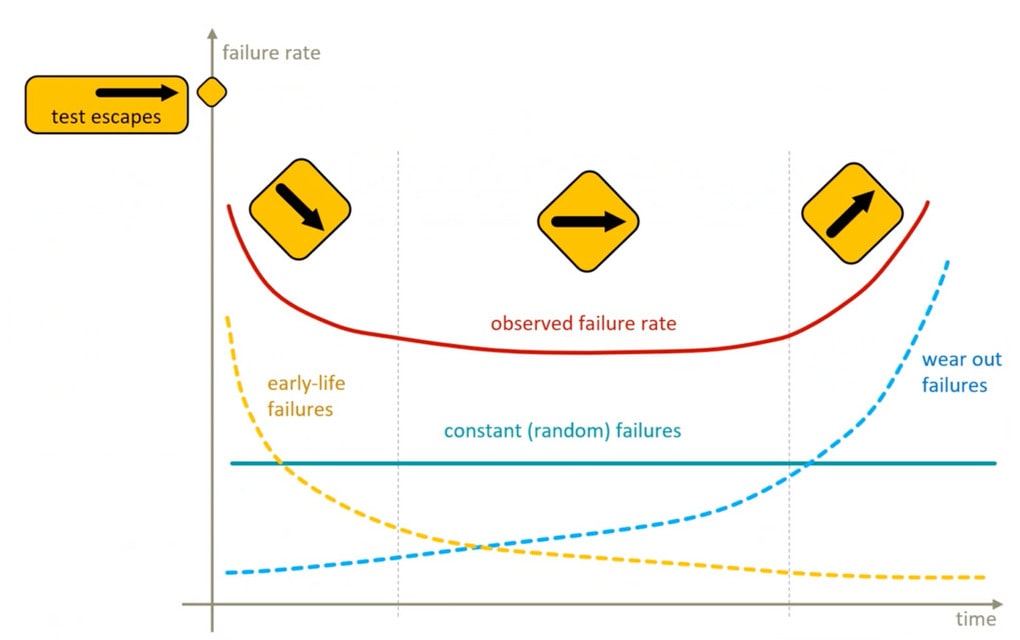

Arteris Empowering Advances in Inference AcceleratorsSystolic arrays, with their ability to highly parallelize…Read More The Convergence of Functional with Safety, Security and PPA VerificationFormal For All! “Do I need a PhD…Read More

The Convergence of Functional with Safety, Security and PPA VerificationFormal For All! “Do I need a PhD…Read MoreHDMI vs DisplayPort?… DiiVA is the answer from China!

During the early 2000’s, when OEM starting to question the use of LVDS to interface with display devices, two standards has emerged: High-Definition Multimedia Interface (HDMI) and DisplayPort. HDMI has been developed by silicon Image, surfing on the success of Digital Video Interface (DVI), and was strongly supported… Read More

Smartphones in the BRICs

The latest edition of GSA Forum has an article by Aveek Sarkar of Apache on system design for emerging market needs. The BRIC (Brazil, Russia, India, China) type countries are characterized by a small rich segment, a large and growing middle class and a large poor segment. One big trend is that smart phone use is expanding very fast.… Read More

OpenAccess

Probably everyone knows that openAccess is a layout database. It was originally developed at Cadence (called Genesis) but has since been transferred to Si2. Strictly speaking, openAccess is actually an API and the database is a reference implementation. The code is licensed under a sort of halfway to open-source: you can use … Read More

Can Your Router Handle 28 nm?

With the adoption of the 32/28 nm process node, some significant new challenges in digital routing arise—including complex design rule checking (DRC) and design for manufacturing (DFM) rules, increasing rule counts, very large (1 billion transistor) designs. To meet quality, time-to-market, and cost targets, design teams… Read More

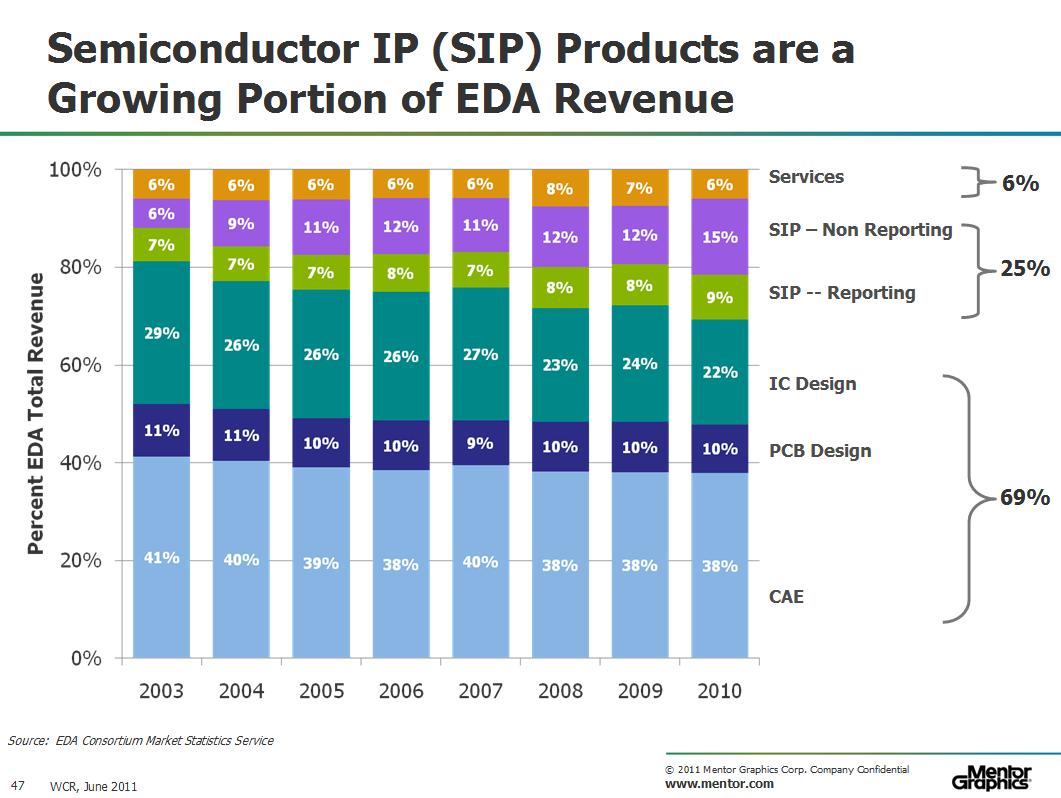

Semiconductor IP State of the Union

After the mega IP acquisitions last year by Cadence (Denali) and Synopsys (Virage) a lot of people are wondering what is next for the commercial Semiconductor IP market. Let me offer my opinion as a person who works closely with foundries and their top customers and the opinion of Dr. Eric Esteve, an expert on interface IP.

The commercial… Read More

Circuit Simulation and IC Layout update from Mentor at DAC

Intro

On Monday evening I talked with Linda Fosler, Director of marketing for the DSM Division at Mentor about what’s new at DAC this year in circuit simulation and IC layout tools.

Notes

IC Station – old name for IC layout tools

Eldo – Eldo Classic- Cell characterization

– ST is the early customer and teaching customer,… Read More

DRC tool guns for Calibre at DAC

Intro

Across the aisle from the Mentor booth at DAC sat a DRC tool competitor to Calibre. I received an update from Randy Smith of Polyteda on Wednesday afternoon, my last EDA vendor of the week.

Ravi Ravikumar, Randy Smith

Notes

Randy Smith – CEO (February 2011) [former founder is gone]- 1979 at HP developing internal tools

–… Read More

An Affordable 3D Field Solver at DAC

Intro

Massimo Sivilotti, Ph.D of Tanner EDA showed me their 3D field solver in the HiPer PX extraction tool at DAC last week.

Notes

Tool Suites – schematics, layout, SPICE simulation, DRC/LVS

– HiPer PX: 3D Field solvero Layers, dielectrics,

o Finite element analysis

o Boundary element methods

o 2D mode for pattern matching… Read More

Hardware Configuration Management at DAC

Intro

Show me what has changed in my RTL or Schematic since the last time I looked. This task is now automated by Cliosoft with their new hierarchical tool called Visual Design Difference (VDD). Srinath showed me what was new for DAC.

Srinath Anantharaman

Notes

LSI, STMicro – use DesignSync for their DM but use VDD for seeing visual… Read More

More Headwinds-CHIPS Act Chop?- Chip Equip Re-Shore? Orders Canceled & Fab Delay