Intro

My Wednesday breakfast at DAC last week was at the Interoperability event sponsored by Synopsys. The Synopsys moderator was so jovial that he reminded me of Jerry Lewis, I was relieved when the guests gave us an update.

Notes

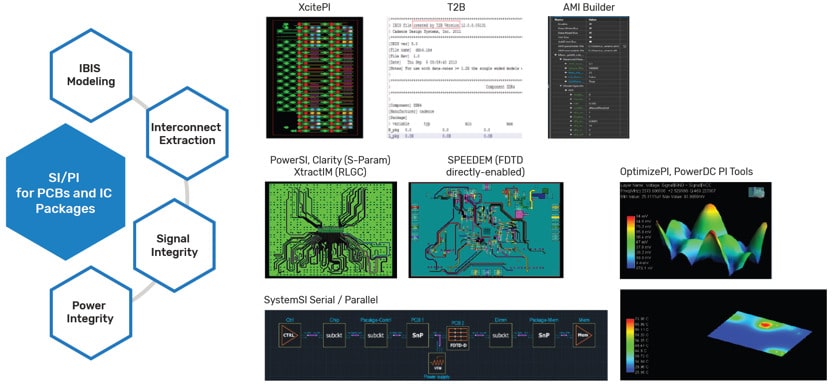

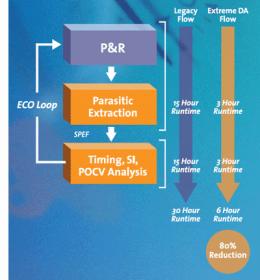

Interconnect Modeling- Open Source Interconnect Technology Format (ITF)o Used by Star RC

–… Read More

AI Semiconductor Market