We are all aware that at 28nm and below several types of complex layout effects manifest themselves into the design and pose a herculean task, with several re-spins to correct them at pre-tapeout. It’s apparent that the layout needs to be correct by construction at the very beginning during the design stage.

I will see you at the Substrate Vision Summit in Santa ClaraWIth packaging being one of the top sources…Read More

I will see you at the Substrate Vision Summit in Santa ClaraWIth packaging being one of the top sources…Read More The Immensity of Software Development and the Challenges of Debugging Series (Part 4 of 4)The Impact of AI on Software and Hardware…Read More

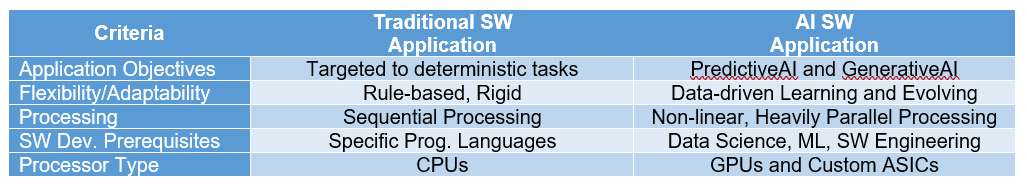

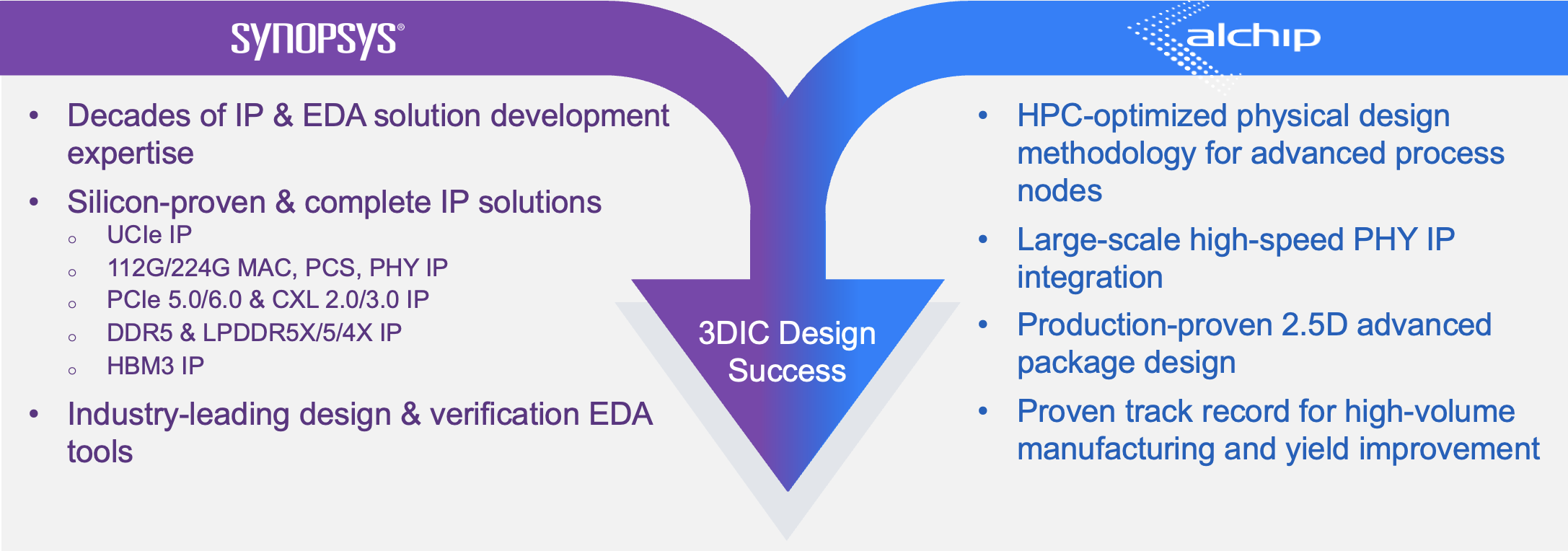

The Immensity of Software Development and the Challenges of Debugging Series (Part 4 of 4)The Impact of AI on Software and Hardware…Read More Alchip is Paving the Way to Future 3D Design InnovationAt the recent TSMC OIP Ecosystem Forum in…Read More

Alchip is Paving the Way to Future 3D Design InnovationAt the recent TSMC OIP Ecosystem Forum in…Read More20nm IC Design at IBM using Cadence Tools

Collaboration between EDA, Foundry and Design was the key idea today in a webinar hosted by IBM and Cadence about 20nm custom IC design. The three presenters were:

John Stabenow, Cadence

Jeremiah Cessna, Cadence

Keith Barkley, IBM… Read More

The Biggest EDA Company You’ve Never Heard Of

There’s this EDA company. They have over 100 tapeouts. They have a $28M in funding. They have 250 people. And you’ve never heard of them. Or at least I hadn’t.

They are ICScape. They started in 2005 with an investment from Acorn Campus Ventures and delivered their first product, ClockExplorer, in 2007 and their… Read More

Use a SpyGlass to Look for Faults

There is a famous quote (probably attributed to Mark Twain who gets them all by default) “When looking for faults use a mirror not a spyglass.” Of course if you have RTL of your IP or your design then using a SpyGlass is clearly the better way to go. But it is getting even better since there is a new enhanced release, SpyGlass… Read More

Smart mobile SoCs: NVIDIA

When the name synonymous with personal computer graphics decided to turn their engineering talent toward the mobile business, heads turned. NVIDIA has rather quickly gained a foothold in tablets by squeezing four high performance processing cores, twelve graphics cores, and more onto a Tegra 3.… Read More

Carl Icahn Blinks in Bid for Mentor Graphics

One year ago activist investor Carl Icahn started a hostile takeover bid for Mentor Graphics and was able to offer up three new board members, however yesterday we read that Mentor Graphics will:

- Have their annual shareholder meeting on May 30th

- Two of Icahn’s board members are not on the roster for renewal

- Mr. Icahn has no

IC design at 20nm with TSMC and Synopsys

While the debate rages on about 28nm yield at foundry juggernaut TSMC, on Monday I attended a webinar on 20nm IC design hosted by TSMC and Synopsys. Double Patterning Technology (DPT) becomes a requirement for several layers of your 20nm IC design which then impact many of your EDA tools and methodology.… Read More

ARM Models: Carbon Inside

ARM used to build their own models. By hand. They had an instruction-set simulator (ISS) called ARMulator that was largely intended for software development, and cycle-accurate models that were intended to run within digital simulators for development of the hardware of ARM-based systems.

There were two problems with this … Read More

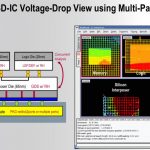

RedHawk: On to the Future

For many, maybe most, big designs, Apache’s RedHawk is the signoff tool for analyzing issues around power: electromigration, power supply droop, noise, transients and so on. But the latest designs have some issues: they are enormous (so you can’t just analyze them naively any more than you can run a Spice simulation… Read More

Book Review – Quantum Physics: A Beginner’s Guide

It’s been 34 years since I graduated from the University of Minnesota with a degree in Electrical Engineering so I was curious about what has changed in quantum physics since then. Alastair Rae is the UK-based author who wrote the book – Quantum Physics: A Beginner’s Guide. I read this on my Kindle Touch e-book… Read More

More Headwinds – CHIPS Act Chop? – Chip Equip Re-Shore? Orders Canceled & Fab Delay