You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Global Design Closureby Paul McLellan on 01-09-2013 at 8:34 pmCategories: EDA

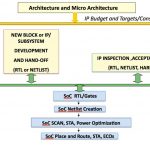

Satish Soman, chief solutions architect at Atrenta, was invited to give a presentation on Global Design Closure at the VLSI India conference in Pune at the start of this month. He talked about the need to close the gap between the typical SoC development methodology and what happens in reality.

SoCs are really put together in two … Read More

This morning I spoke with Mahesh Tirupattur, Executive VP of Analog Bits about IC design challenges and using EDA tools to create high performance, mixed-signal semiconductor IP.

… Read More

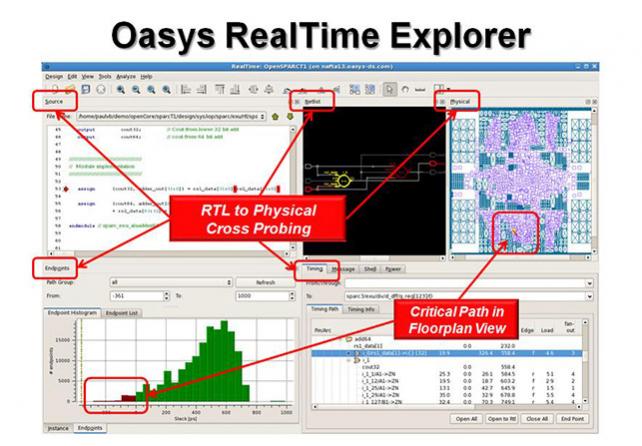

The current methodology in design in most companies, and certainly many of the biggest, is that front end RTL design is done by one team with a limited set of front-end design tools. This is then eventually passed off to the physical design team who run all the scripts, do the “real” synthesis, place & route and timing… Read More

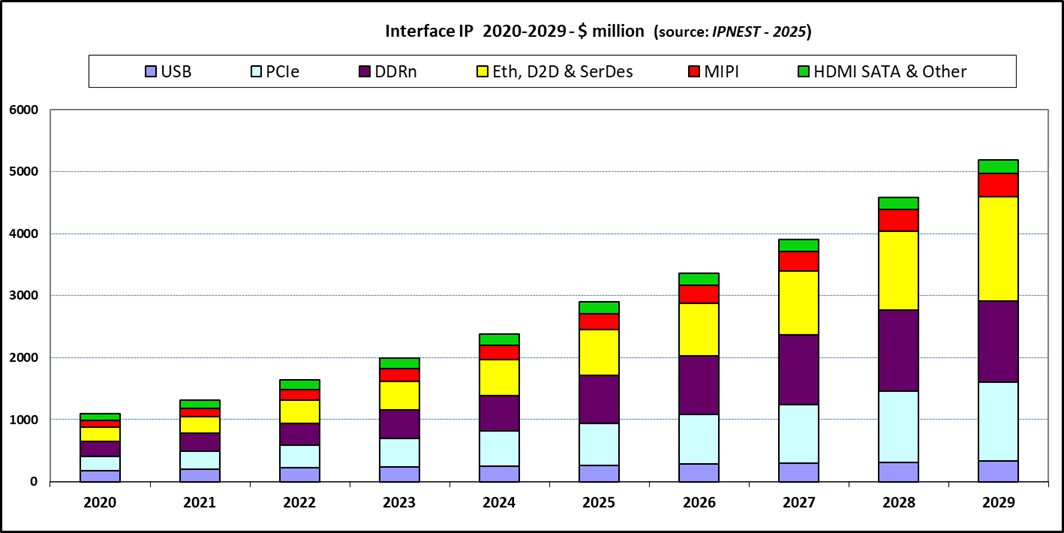

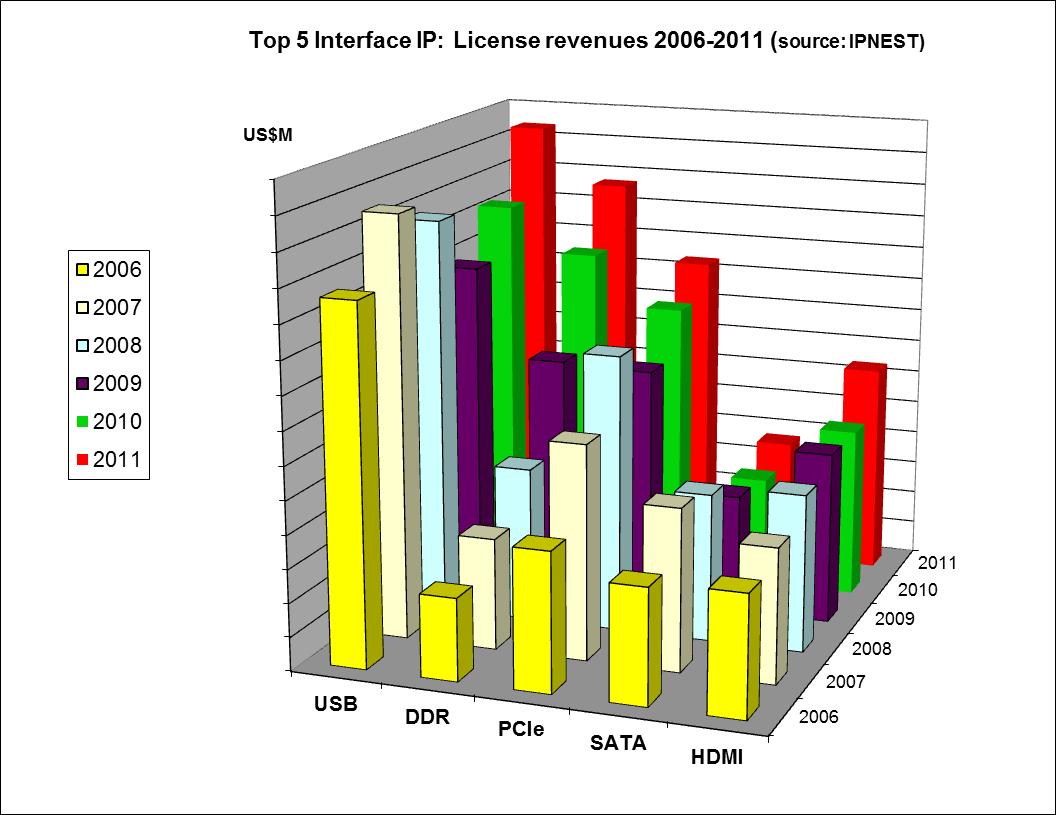

Who makes the decision and declare that a specific interface protocol is successful? Not me, as I can only consolidate market share data and some insight information coming from the industry. The end user, when going to a shop (real or virtual) and spend a significant part of his budget to buy an electronic product, selecting among… Read More

Sidense will be exhibiting at the Common Platform Technology Forum in Santa Clara, California on February 5, during which time they will be discussing their one-transistor, one-time programmable (1T-OTP) memory IP products. Based on their patented 1T-Fuse™ bit cell, Sidense antifuse-based 1T-OTP macros offer a secure, reliable,… Read More

“It’s not like we started it,” said Larry. “After all the idea of going Thermonuclear was first broached by Steve to Eric at their outdoor café meeting in Palo Alto way back in 2010. We’re just following by example and as Steve was wont to quote Picasso; “good artist copy, great artist steal” so why not go Thermonuclear with our Android… Read More

Time to pack up for the 2013 Consumer Electronics Show in Las Vegas, I will be driving down with my beautiful wife Shushana because she does not like to fly. The drive takes the better part of a day so we will leave early and see the sunrise over the desert. She is great company, the time will fly by. We will be 2 of the more than 150,000 people… Read More

I love all things SPICE so when I read a tweet tonight from @PartSimI just had to try out their Schematic Capture and SPICE circuit simulator in a browser. The site is www.partsim.com and all you need is a web browser and short registration process, then it’s off to the Examples where I found a simple CMOS inverter and then extended… Read More

The Common Platform Alliance — IBM, Samsung Electronics, Co., Ltd., and GLOBALFOUNDRIES — continues to redefine the landscape of the semiconductor industry with its groundbreaking collaboration. Join us at our 2013 Common Platform Technology Forumon Tuesday, February 5, 2013 at the Santa Clara Convention Center as we showcase… Read More

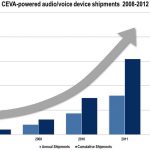

When mentioning CEVA DSP IP cores, the first reaction is to think about the complexes DSP functions used into wireless Modem Application like 3G and Long Term Evolution (LTE). Considering that CEVA market share is above 70% for these products, such a reaction makes sense. But did you knew that CEVA DSP IP cores are also empowering… Read More

TSMC N3 Process Technology Wiki