More details are now available for the EDA 50[SUP]th[/SUP] anniversary event on October 16[SUP]th[/SUP]. If you have not been to the museum lately this is a must see event as it is all new. Definitely check out the auction items! Just do not bid against me or it will get very expensive for one of us. I’m watching Storage Wars reruns so… Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read More

Enabling Next-Generation AI Through Advanced Packaging and 3D Fabric IntegrationThe rapid rise of artificial intelligence is fundamentally…Read MoreCadence Grows VIP Business – What’s New?

VIPs (Verification IPs) are really important in this complex world of SoCs which involve various IPs, interfaces and continuously evolving protocols and standards, thus making the task of verifying an overall system extremely challenging. And the verification must be done in minimum possible run-time and memory consumption.… Read More

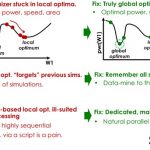

High-Sigma Standard Cell Optimization!

Standard cell optimization is an important problem, because the speed, power, and area of cells has a direct impact speed, power, and area of the whole chip. Typically, standard cell optimization been done with simple in-house local-optimizer scripts. However, these optimizers have had several flaws: they don’t properly capture… Read More

A Mixed-Signal IC Summit in San Jose

Analog and mixed-signal ICs are tougher to design and verify compared to digital, so if you want to learn more about best practices from actual AMS engineers then consider attending a summitthat is sponsored by Cadence Design Systems next Thursday, October 10th in San Jose from 8:00AM until 6:30PM.

They’ve lined up an interesting… Read More

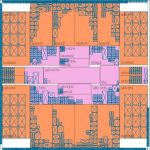

Floorplanning Merged With Synthesis

One area of iteration that is becoming more problematic is between floorplanning and synthesis. So much of timing is driven by placement that fixing timing and even power often involves not just re-synthesis and re-placement but alterations to the floorplan. The Achilles heel of existing methods is that floorplanning tools … Read More

TSMC Awards Berkeley Design Automation

One of the highlights of the TSMC 2013 Open Innovation Platform® Forum was the Partner Award Ceremony. TSMC awarded Berkeley Design Automation (BDA) with the TSMC Open Innovation Platform’s Partner of the Year Award 2013 for joint development of 16nm FinFET design infrastructure. I talked with Ravi Subramanian, BDA CEO,… Read More

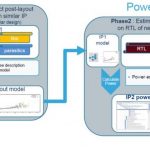

Architecture-level Power Modeling Methodology at Samsung

At DAC this year there was a presentation from Samsung titled, “Profile-based Architecture Power Modeling Methodology for AP/SoC Product”. I’ve been using Samsung Smart Phones for the past four generations, so was very curious about how they have managed to improve the average battery life from less than… Read More

Sequential Equivalence Checking with Jasper

When new restaurants open they sometimes have what is called a ‘soft opening’ where they open a few days earlier than the official opening night. They are less busy since nobody knows they are open yet, maybe the whole menu isn’t available and expectations may be lower. Of course, Broadway productions also often… Read More

ST Endorses PowerArtist with ARM Cores & FDSOI libs

It was an interesting webinar I attended, presented by STMicroelectronicson how they are benefited in power saving and thermal dissipation by using FDSOI technology and also by using PowerArtist in their design. So, it’s an advantage from both sides – semiconductor technology and semiconductor design tool. It’s worth attending… Read More

Stick to the script for repeatable FPGA-based prototyping

70% of today’s ASIC and SoC designs are being prototyped on FPGAs. Everybody knows that. But, did you know that automating the process of converting what could be thousands of ASIC “golden” files into FPGA-friendly versions can mean big savings in a large design?… Read More

Solving the EDA tool fragmentation crisis