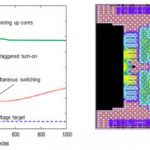

Altera announced in February that they would be using Intel as a foundry at 14nm. Historically they have used TSMC. Then in June they announced the Stratix 10 family of FPGAs that they would build on the Intel process. At the Globalpress summit in May I asked Vince Hu about their processor strategy. Here is what I wrote about itat the… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreDiagnosing Double Patterning Violations

I’ll bet you’ve read a bunch of stuff about double patterning, and you’re probably hoping that the design tools will make all your double patterning issues just go away. Well, the truth is that the foundries and EDA vendors have worked really hard to make that true.

However, for some critical portions of your design, there … Read More

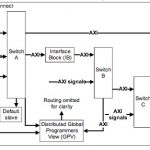

Getting the Most Out of the ARM CoreLink™ NIC-400

SoC designers are attracted to ARM as an IP provider because of their popular offerings and growing ecosystem of EDA partners like Carbon Design Systems. At the upcoming ARM Techcon on October 31 this week in Santa Clara you’ll have an opportunity to hear a joint presentation from ARM and Carbon Design Systems on: Getting … Read More

Cadence’s Mixed-Signal Technology Summit

On October 10, I attended another Cadence Summit, this one titled the Cadence Mixed-Signal Technology Summit. Recently, I had written about the Cadence Silicon Verification Summit. The verification event was the first of its kind, and I thought it had terrific content. Being more of a digital guy myself, I was unaware that Cadence… Read More

Smartphones Are More Amazing That You Can Believe

I’ve written before about just how widespread mobile phones are: more people use mobile phones that a a toothbrush and more know how to use one than to use a pencil to write. This all happened very recently. I bet if you are asked when you got your first mobile phone you will guess too early. I had a car-phone in 1993 and a real mobile… Read More

Let’s comment… a comment from Sonics (about Arteris)

We still don’t know the precise status about a potential acquisition of Arteris by Qualcomm, and I prefer not to comment a rumor and wait for the official announcement, if any. But I would like to comment … a comment about this rumor, recently made by Sonics. This comment has taken the form of an Open Letter, from “Grant Pierce, CEO of… Read More

Open Letter from Sonics to Arteris

I don’t remember seeing an open letter from one EDA or IP company to another until today. Sonics have published an open letter to Charlie Janac, the CEO of Arteris. What seems to have happened is that Arteris have sold their assets to Qualcomm and the development team (which is based in France) and several AEs are already Qualcomm… Read More

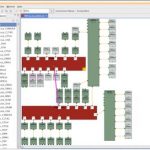

Strategic Analog IP Power Management for SoCs

This tutorial describes how analog IP is becoming more important in any power management strategy and shows the major analog building blocks to manage power and temperature in a SoC on leading edge technology nodes.

The tremendous demand for high-performance computing devices has led to aggressive technology scaling, allowing… Read More

An easier way to deal with design rule waivers (video)

At advanced nodes, design rules are necessarily more complex and restrictive. Although most of the time you can find a way to live with them, sometimes it’s necessary to seek a waiver from the foundry for a particular design feature. This involves documenting the feature, the design rules in question and the conditions under which… Read More

An Affair to Remember: EDA’s 50th Anniversary

What an amazing night! I celebrated the 50[SUP]th[/SUP] anniversary of the industry I grew up in! With my beautiful wife at my side and a table full of friends we all went down memory lane, ate, drank, and then enjoyed the auction.

The tour of the new computer museum was amazing. I was learning so much up until the 1970’s, then … Read More

ASML High-NA EUV is Not Ready for High-Volume Production