In case you haven’t noticed, Synopsys has been in the press lately talking about their relationship with TSMC. Since I’m an internationally recognized industry expert they gave me a call for a briefing and I was happy to do it. Staying connected with the #1 EDA company is important and fun since I get to ask questions that most people… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

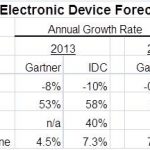

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreTablets, smartphones & China still driving growth

Media tablets and smartphones have been the two most significant drivers of electronics and semiconductor growth for the last few years. Forecasts from two major market research firms indicate these devices will continue to be major drivers for the next few years. For 2013, Gartner and IDC (International Data Corporation) both… Read More

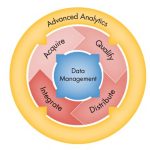

Webinar on IP Lifecycle Management

EDA and Semiconductor companies are offering new webinars almost every week of the year, so there’s always something worth learning about that only takes an hour of time. On November 5th there’s an interesting webinar planned on the topic of IP Lifecycle Management, hosted by Methodics. I blogged two weeks ago about,… Read More

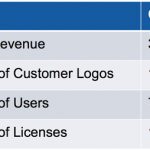

Kathryn: "Formal Will Dominate Verification"

At the Jasper Users’ Group meeting, Kathryn presented the state of Jasper. The numbers are impressive. The company has grown at a CAGR of over 35% since 2007, which is 6 times faster than EDA as a whole. They have been profitable at 15-20% EBITDA for 14 consecutive quarters.

Jasper is focused on engaging deeply with a small number… Read More

3DIC, the World Goes to…Burlingame

For the tenth year, the big 3DIC conference takes place in the Hyatt Regency at Burlingame (just south of San Francisco Airport). Officially it is 3D Architectures for Semiconductor Integration and Packaging or ASIP. This year there have already been some significant 3D announcements: TSMC’s 3D program, and Micron’s… Read More

Hierarchical Clock Domain Crossing

One of the first blogs I wrote on SemiWiki was on clock domain crossing (CDC). I thought it was rather a specialized subject, a sort of minority interest. It turned out to be one of the most-read blogs I’ve written. Modern SoCs have lots of unrelated clocks, maybe hundreds, and so ensuring that signals going from one clock domain… Read More

Qualcomm start selling DSP IP core?…

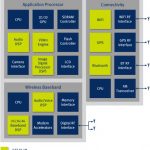

In recent times semiconductor companies have revealed their intentions to license their in-house processor architectures for the first time – IBM want to license their Power CPU architecture, nVidia to license their GPU architecture. Most recently, a rumor has surfed: Qualcomm will license their DSP architecture. We should… Read More

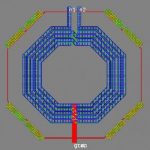

EM Solver and Visualization Essential for Device Design

In many designs, an on chip inductor is created as though it were simply a device with an L and a Q value. Of course this view would seem to make life simpler for designers and the tools they use. But in reality even a simple inductor is really a complex compound structure with many electromagnetic elements interacting in complex ways.… Read More

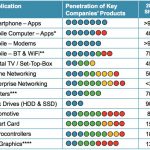

ARM Signs 48 New Licenses in Q3

ARM announced their quarterly results early this morning. ARM’s results are a funny mixture of backward looking information such as royalties which are reported a quarter late since they have to wait for their licensees to work out how many they shipped, and some very forward looking such as new licenses, which bring some… Read More

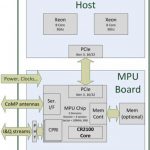

Cloud-RAN: a New Way to Build a Basestation

One thing that I learned about at the Liney Microprocessor Conference last week was C-RAN which stands for Cloud Radio Access Networks. The technology is created by ASOCS who are working with China Mobile as the driving customer. And before you dismiss that as just being one network interested in the technology, China Mobile has… Read More

ASML High-NA EUV is Not Ready for High-Volume Production