This will be my 30[SUP]th[/SUP] Design Automation Conference. I know this because my first DAC was the same year I got married and forgetting how many years you have been married can cost you half your stuff. I have known Cliff Hou for half of that time and he has proven to be one of the most humble and honorable men I have worked with, definitely.… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreSpeeding Up AMS Verification by Modeling with Real Numbers

My first introduction to modeling an AMS behavior using a language was back in the 1980’s at Silicon Compilers using the Lsim simulator. Around the same time the VHDL and Verilog languages emerged to handle the modeling of both digital and some analog behaviors. The big reason to model analog behavior with a language is for… Read More

Power Control Moving into Hardware

Sonics have been building networks-on-chips (NoCs) for a long time and have amassed a rich patent portfolio. So being granted a new one isn’t usually deemed press-release-worthy. However, their latest patent on power management is pretty significant. It is patent 8,601,288 titled “Intelligent Power Controller”.

Historically… Read More

Happy Birthday Xilinx

I have never done this before, wished a company happy birthday. So here goes, Happy Birthday Xilinx! How does it feel to be 30? Looking good eh? Signing up for AARP? My family and I just sang and had cake and ice cream. They did look at me like I was nuts when I set a place at the table for a Xilinx FPGA. In all seriousness, over the years Xilinx… Read More

ISO 26262 driving away from mobile SoCs

Connected cars may be starting to resemble overgrown phones in many ways, but there are critical differences now leading processor teams in a different direction away from the ubiquitous mobile SoC architecture – in turn causing designers to reevaluate interconnect strategies.

The modern car has evolved into a microcontroller… Read More

Quoting Automatically the eSilicon Way

Every ASIC company has a major challenge: they have to work out what it is going to cost to build the customer’s product and commit to deliver it at that price. Too high and you lose the business. Too low and you will wish you’d lost the business. Historically this has been done largely manually. This is an expensive process.… Read More

Will Google Design Server SoCs?

Google is search, of course, but it is also OS (Android), systems (Glass) and increasingly, maybe, hardware. Rumors are swirling that through careful acquisitions and focused internal development, Google is set to make its own server SoCs.

Google’s Larry Page has stated that they are in the hardware business. They’ve been making… Read More

I switched to Aldec Active-HDL

I have written this before, but I was a ModelSim snob. That has changed after trying Active-HDL from Aldec. I have no plans on going back to ModelSim. You ask why? Well astute reader, great question. Unfortunately these blogs are text limited and there is no way to write about all the bells and whistles of Active-HDL. So before I continue,… Read More

Intel 14nm Delayed Again?

From the sources in which I confirmed the last Intel 14nm delay, I just confirmed another. Intel 14nm is STILL having yield problems. Remember Intel bragging about 14nm being a full node and deriding TSMC because 16nm is “just” 20nm with FinFETs added? Judging by the graph, clearly FinFETs are not the problem here. … Read More

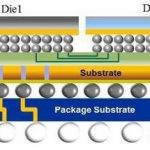

Smart Strategies for Efficient Testing of 3D-ICs

3D-IC has a stack of dies connected and packaged together, and therefore needs new testing strategies other than testing a single die. It’s given that a single defective die can render the whole of 3D-IC unusable, so each die in the stack must be completely and perfectly tested before its entry into that stack. Looking at it from a … Read More

ASML High-NA EUV is Not Ready for High-Volume Production