We are not talking about ARM Ltd., as the IP vendor has already passed the $1B sales in 2013. In fact, we are not talking about a single IP vendor; this $1B mark will be passed by two IP market segments: Interface and Verification IP. In fact these two segments are very close together. When an IP is developed to support a specific Interface… Read More

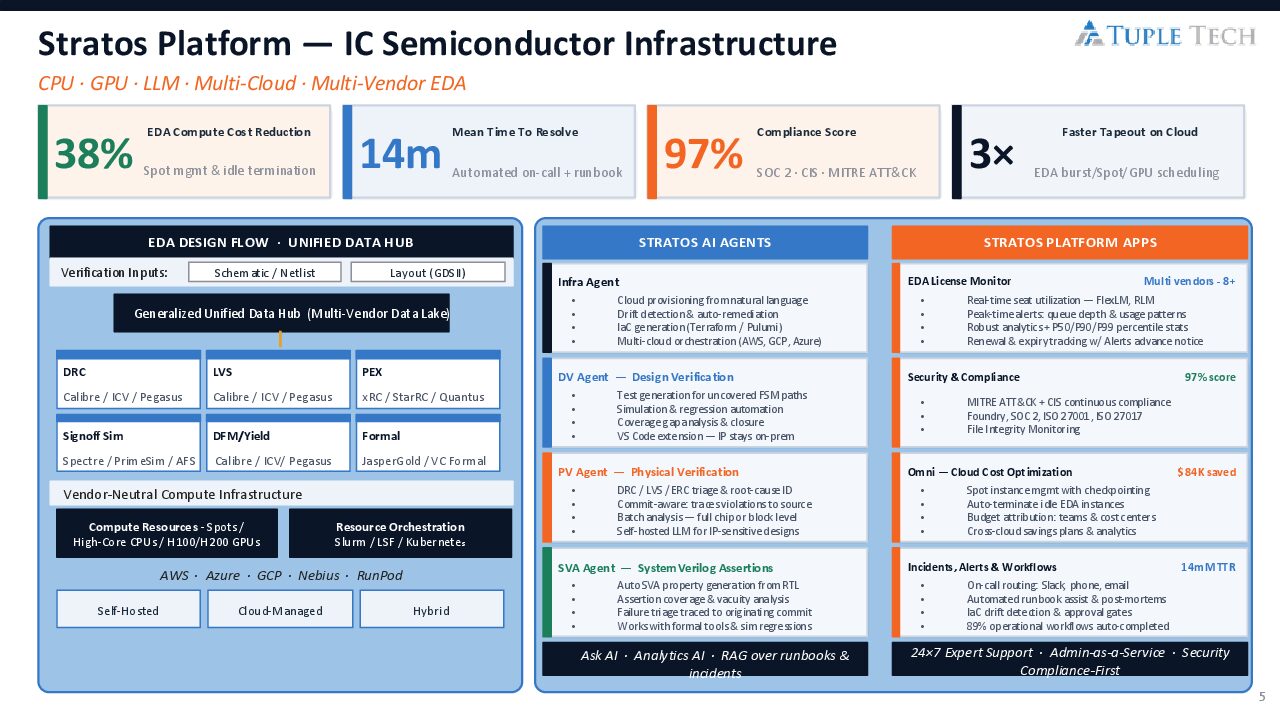

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreSynopsys Acquires Coverity

Synopsys announced this afternoon that they are acquiring Coverity for $375M subject to all the usual reviews.

There are a couple of other big EDA connections. Aki Fujimora, who was CTO of Cadence, is on the board. And Adreas Kuehlmann is the VP of R&D. He used to run Cadence Berkeley Laboratories before moving to the other end… Read More

One SPIE session not to miss

The time is nigh for another meeting of the practitioners of the lithographic arts, dark and otherwise, at the SPIE Advanced Lithography symposium.

I love this conference for the engagement you see, both in the sessions and in the hallways. People actually meet and talk and argue. There’s always interesting gossip, exciting technologies,… Read More

Xilinx: Delivering a Generation Ahead

Last week was Xilinx’s investor day. Xilinx believe they are now a process generation ahead. They did over $100M in 28nm designs in FY2013 (Xilinx FY ended March 2013) and did over over $100M in Q4 2013 calendar year alone (and this is almost all true production volume, with only about 5% prototypes) with a plan greater than … Read More

Brian Krzanich Does Reddit AMA

Do you know what an AMA is on Reddit? It stands for “ask me anything”. A person, often a famous person like Bill Gates (last week) but sometimes just someone who does an interesting job (like astronaut) or was in an interesting situation (like the hijack from Ethiopia last week).

Today, it is someone who argualble is all… Read More

Carbon Design Systems – Secret of Success

Last week, after learning from the press releaseof Carbonabout its rocking sustained growth with record-breaking revenue and a thumping 46% increase in bookings, I was interested to know some more details about what drives Carbon to such an amazing performance in an EDA market that is generally prone to growth of a few percentage… Read More

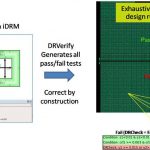

Verifying DRC Decks and Design Rule Specifications

DRVerify is part of the iDRM design rule compiler platform from Sage DA, something that I have been personally involved with for the past three years. DRVerify is mainly used to verify third party design rule check (DRC) decks and ensure that they correctly, completely and accurately represent the design rule specification. In… Read More

The Future of Money is Digital – BitCoin Introduction

By now most people who read or listen to the news know something about Bitcoin (BTC). Most people have the perception that it is either the currency of crime or speculation. Put aside the perceptions and consider this. When is the last time you saw someone write a check in the grocery store, especially someone under 60? Today’s… Read More

Smart cards hard for the US to figure out?

Every once in a while, I just scratch my head and wonder just what in the wide, wide world of tech is going on. More than ever, it seems the big barriers to adoption aren’t a lack of technology – instead, barriers come from a system that staunchly defends the old way of doing things, even when the participants are battered, broken, and … Read More

Verification of Power Delivery Networks

Power delivery networks (PDN) are the metal structures on a chip that delivers the power. In a high-end desktop SoC this might be delivering as much as 150W, and with voltages around 1V that means over 150 amps of current. Clearly getting the PDN correct is critical for a correctly functioning chip. One of the challenges to verifying… Read More

Siemens U2U 3D IC Design and Verification Panel