Today Xilinx announced SDAccel, an initiative for the data-center. This is the second of a series of software defined development initiatives for various markets, the first being SDNet that is targeted at building networking applications. One challenge that a company like Xilinx faces is that as the scale of design move up to … Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More

Bringing mathematical rigour in the world of hardware - a journey into Formal VerificationThis interview presents the first steps of Robert…Read More The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More

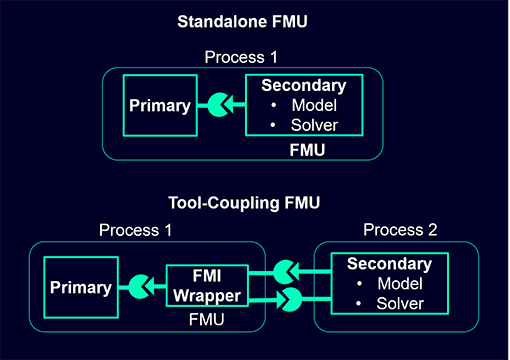

The Great Divide: A Tale of Three Hardware Emulation ArchitecturesHardware emulation arose as a necessity out of…Read More A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More

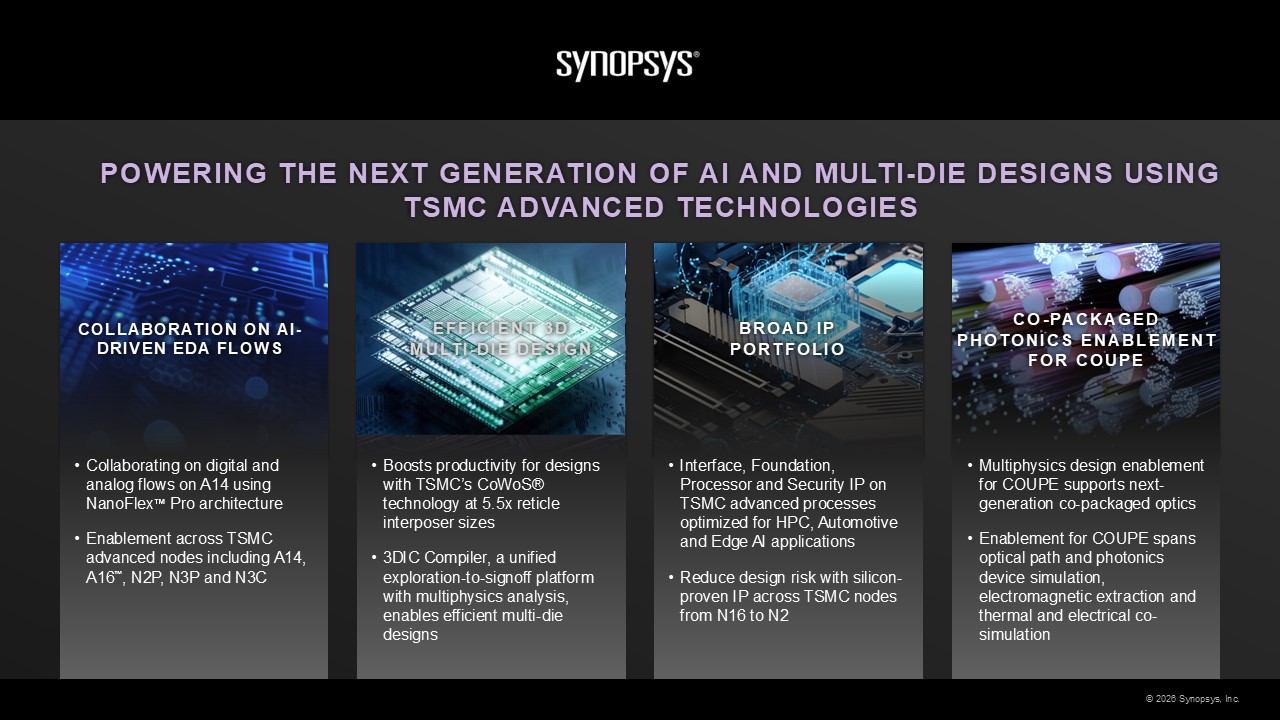

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More

Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read MoreSemiconductor IP Make the World Go Round!

Semiconductor IP really does make the life of a semiconductor professional much easier which is why Google brings us so much IP traffic. If you look at the SemiWiki analytics, IP has always been a top draw. In comparison to standard EDA traffic, IP gets about 25% more views per blog on average. Synopsys is not only the leading EDA company… Read More

Complete SoC Debugging & Integration in a Single Cockpit

These days it’s common to expect large digital designs, analog blocks, custom IPs, glue logic, interfaces and interconnects all developed separately, perhaps by different vendors / teams, but integrated together in a single environment forming an SoC. The SoC can have multiple clock domains and can work in multiple modes of … Read More

Are you SmarCoT or IoT?

No need to explain the IoT acronym (Internet of Things) except that IoT doesn’t really describe a reality: do you really know about any “Thing” being directly connected to the Internet? In fact, there is probably some intermediate system linking this thing with the Cloud, like a smartphone, an Internet box, a PC, etc. Just take a … Read More

SEMI Industry Strategy Symposium, Half Moon Bay

Every January SEMI runs its Industry Strategy Symposium which is held at the Ritz Carlton in Half Moon Bay. This time it is January 11-14th. It is subtitled Riding the Wave of Silicon Magic.

I find it a fascinating event to attend. There is a lot of information to be had in the presentations, of course, but also a lot from talking to attendees.… Read More

Semiconductor IP Information Flow!

One of the biggest challenges in the IP business, or any other business for that matter, is managing the information flow. Semiconductor IP is a critical piece of the fabless semiconductor ecosystem so anybody and everybody can write about it. Unfortunately, anybody and everybody ARE writing about it. From day one IP has been a … Read More

NoC 101, a Sonics Webinar

One of the things that I’ve been telling the people at Sonics when they will listen is that they should do a bit more basic education on Networks on Chip (NoC). Sure, the people who actually use Sonics’s products care about deep details such as security and power management, but there is a whole host of designers who have… Read More

How many 28nm FDSOI SoC Design Starts in 2015? In 2020?

I would like to further discuss this graphic (presented during IP-SoC 2014 by John Koeter, VP of Marketing IP and prototyping, Synopsys) and focus on Active Design and Tapeouts at 28nm. In fact the very first activity appeared in Q1 2007, but it was only during 2010 that 28nm become popular, after the first Tapeouts coming in Q1 and… Read More

Can Android1 Lead the Way for Google in New Smartphone Market?

I had been wanting to write about it since Google’sbig bang announcement of Android1 in India in Sep this year and their associated strategy to capture some of the large pockets of Smartphone market within a matured or declining cell phone market and maturing overall market of Smartphone. Since I wrote my last article hereon maturation… Read More

IP-SoC 2014 Top Class Presentations…

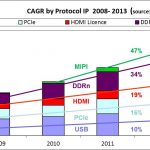

… were given to an ever shrinking audience. This is IP-SoC paradox: audience has enjoyed very good presentations made by Cadence, Synopsys or ST-Microelectronic, to name just a few. As far as I am concerned, I was happy to present the “Interface IP Winners and Losers (Protocols)” in the amphitheater during the first day, enjoying… Read More

Siemens U2U 3D IC Design and Verification Panel