In a previous post we discussed a few automotive applications that will be big markets for GaN technology. But this is just a small part of the GaN story!

GaN transistors such as eGaN FETs from EPC are today available with performance 10 times better than the best commercial silicon. What happens when several devices are integrated… Read More

The 71st International Electron Devices Meeting (IEDM 2025)It is hard to believe this conference is…Read More

The 71st International Electron Devices Meeting (IEDM 2025)It is hard to believe this conference is…Read More TSMC’s 2026 AZ Exclusive Experience Day: Bridging Careers and Semiconductor InnovationIn February of 2026, Taiwan Semiconductor Manufacturing Company…Read More

TSMC’s 2026 AZ Exclusive Experience Day: Bridging Careers and Semiconductor InnovationIn February of 2026, Taiwan Semiconductor Manufacturing Company…Read More DAC – The Chips to Systems Conference 2026The Design Automation Chips to Systems Conference is…Read More

DAC – The Chips to Systems Conference 2026The Design Automation Chips to Systems Conference is…Read More Taming Advanced Node Clock Network Challenges: JitterClock jitter rarely fails in obvious ways. In…Read More

Taming Advanced Node Clock Network Challenges: JitterClock jitter rarely fails in obvious ways. In…Read MoreThe Case for Data Management Amid the Rise of IP in SoCs

In the late 1990s and early 2000s, during the adolescent days of the system-on-chip (SoC) design movement, there was a lot talk about IP and design reuse, but it was seldom put into practice. A decade later, SoC turned into a juggernaut with a tripartite alliance of chipmakers, IP suppliers and semiconductor manufacturing fabs.… Read More

Threat Detection: How To Keep the Crown Jewels Secure

Let’s just take it as a given that securing IP design data is critical. It’s rather like saying that it’s a good idea to have security in the Tower of London to stop the crown jewels being stolen. IP blocks are the crown jewels of an SoC company.

Data now must be secured within the collaborative teams that share that… Read More

SoC and Foundry Update 2H 2015!

Rarely do I fly first class but I did on my recent trip to Asia. It was one of the new planes with pod-like seats that transforms into a bed. The flight left SFO at 1 A.M. so I fell asleep almost immediately missing the first gourmet meal. About half way through the flight I found myself barely awake staring straight up and what do I see? STARS!… Read More

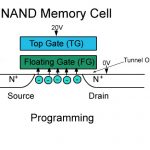

Adding NAND Flash Can Be Tricky

As consumers, we take NAND flash memory for granted. It has worked its way into a vast array of products. These include USB drives, SD cards, wearables, IoT devices, tablets, phones and increasingly SSD’s for computer systems. From the outside the magic of flash memory seems quite simple, but we have to remember that this is a technology… Read More

TSMC is the Top Dog in Pure-Play Foundry Business

We all have echoed the fact that the arrival of fabless business model in the semiconductor industry has transformed it completely. The book, “Fabless: The Transformation of the Semiconductor Industry” provides several stories around that. In the backdrop of that, one key point to ponder upon is the start of pure-play foundries;… Read More

Solido Wrote the Book on Variation

When I studied mathematical analysis, one of the things that we had to prove turns out to be surprisingly difficult. If you have a continuous function and at one point it is below a line (say zero) and at another point it is above zero, then there must be a point at which the value is exactly zero. In effect, a continuous function can’t… Read More

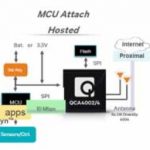

Xtensa core in Qualcomm low-power Wi-Fi

Wi-Fi has this reputation as being a power hog. It takes a relatively big processor to run at full throughput. It is always transmitting all over the place, and it isn’t very efficient at doing it. Most of those preconceived notions arose from older chips targeting the primary use case for Wi-Fi in enterprise and residential environments.… Read More

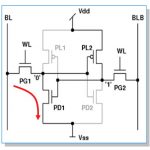

Optimizing SRAM IP for Yield and Reliability

My IC design career started out with DRAM at Intel, and included SRAM embedded in GPUs, so I recall some common questions that face memory IP designers even today, like:

- Does reading a bit flip the stored data?

- Can I write both 0 and 1 into every cell?

- Will read access times be met?

- While lowering the supply voltage does the cell data retain?

Michael Sanie Plays the Synopsys Verification Variations

I met Michael Sanie last week. He is in charge of verification marketing at Synopsys. I know him well since he worked for me at both VLSI Technology and Cadence. In fact his first job out of college was to take over support of VLSIextract (our circuit extractor), which I had written. But we are getting ahead.

Michael was born in Iran and… Read More

The Risk of Not Optimizing Clock Power