I cut my teeth in silicon IC design at Texas Instruments during the early 1980’s working on what would eventually become the ASIC and Fabless IC industries that enabled the explosive growth of the electronics industry over the last three decades. Of late I’ve become involved in the silicon photonics space and I am getting an incredible… Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More

From the Selfie to Samantha: The Next Trillion-Dollar BehaviorAt CES 2026, Samsung called it a “companion.”…Read More TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More

TSMC’s Record Tool Orders Hint at Another CapEx ShockwaveTSMC’s latest Board of Directors capital appropriation announcement…Read More CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More

CEO Interview with Nagesh Gupta of llmda.aiNagesh has built a career spanning multiple aspects…Read More The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read More

The "New Shift-Left": Why FPGA Prototyping is the Ultimate RISC-V IP SandboxIn the EDA world, "Shift-Left" has traditionally been…Read MoreHyundai Artificial Intelligence Connected Car Insights from Patents

Hyundai announced its plan to develop smart car implementing artificial intelligence (AI) and V2X (vehicle-to-vehicle (V2V) and vehicle-to-infrastructure (V2I)) communication capability. US9159231 illustrates that Hyundai smart car will collect and transmit neighboring traffic information through the V2V communication.… Read More

Roger Rabbit Redux – Self-Driving Car Edition

With General Motors investing $500M in Lyft and buying Cruise Automation (aftermarket self-driving car technology) for $1B, there are some people speculating that the company may be recreating its mid-prior-century effort to monopolize mass transportation. In the 1940’s, National City Lines and Pacific City Lines,… Read More

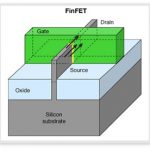

The Importance of Transistor-Level Verification

According to the IEEE Std 1012-2012, verification is the acknowledgement that a product is in satisfactory condition by meeting a set of rigorous criteria. [3] Transistor-level verification involves the use of custom libraries and design models to achieve ultimate performance, low power, or layout density. [2] Prediction… Read More

Book Review Mobile Unleashed The History of ARM

After having taken a closer look at x86 processor with “Inside The Machine” I came across “Mobile Unleashed“, a book about the history of a non-Silicon Valley company and technology for a change that has significantly shaped the world of computing as we know it today: ARM.

Written by Daniel Nenni and Don Dingee the book tells the story… Read More

Webinar alert – Taking UVM to the FPGA bank

UVM has become a preferred environment for functional verification. Fundamentally, it is a host based software simulation. Is there a way to capture the benefits of UVM with hardware acceleration on an FPGA-based prototyping system? In an upcoming webinar, Doulos CTO John Aynsley answers this with a resounding yes.… Read More

Webinar alert – Smart homes demanding low power Wi-Fi

There are two camps of thinking on the IoT: those who believe Bluetooth and Wi-Fi rule the edge, and those who support any of dozens of other wireless networking specifications for their various technical advantages. The ubiquity of Wi-Fi in homes helps devices connect in a few clicks – so why don’t more IoT designers use it?… Read More

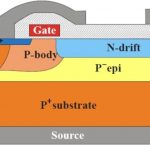

3D TCAD Simulation of Silicon Power Devices

Process and device engineers are some of the unsung heroes in our semiconductor industry that have the daunting task of figuring out how to actually create a new process node that will fit some specific, market niche with sufficient yield to make their companies profitable and stand out from the competition. One such market segment… Read More

Mobile Unleashed…Reviewed

I finished reading Don Dingee and Dan Nenni’s book, Mobile Unleashed, the Origin and Evolution of ARM Processors in Our Devices. I guess by way of disclosure I should say that Don and Dan both blogged with me here on SemiWiki for several years before I joined Cadence, and Dan’s last book Fabless was co-authored with me… Read More

Fabless vs IDM for Data Centers: Silicon Photonics as a Disruptive Force?

I recently received a copy of a book entitled Silicon Photonics III (Amazon) and while perusing the book I was captured by the first chapter entitled ‘Silicon Optical Interposers for High-Density Optical Interconnects’. The chapter covered the work of a team in Japan on an idea they termed “on-chip servers” and “on-board data … Read More

ASML High-NA EUV is Not Ready for High-Volume Production