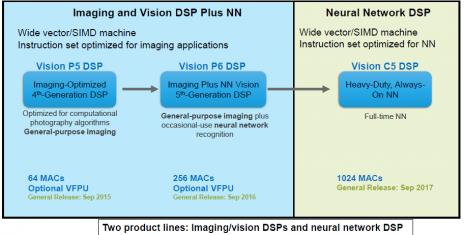

Cadence has recently announced two key design-in for their Vision DSP IP family: MediaTek’s Helio P30 integrates the Tensilica Vision P5 DSP and HiSilicon has selected the Cadence® Tensilica® Vision P6 DSP for its 10nm Kirin 970 mobile application processor. The Kirin 970 being integrated into Huawei’s new Mate 10 Series mobile… Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More RISC-V Now! — Where Specification Meets Scale!In forty plus years as a semiconductor professional…Read More

RISC-V Now! — Where Specification Meets Scale!In forty plus years as a semiconductor professional…Read MoreScale the tools not your expectations

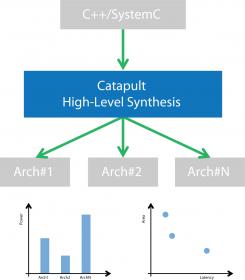

The complexity of silicon chips is exploding. Actually, it has been growing at a tremendous speed for decades. So far, the semiconductor industry has been successful at providing new ways to master new levels of complexity, over and over again.

Standardizing hardware platforms, using higher-level languages with a knowledge… Read More

High-Level Design for Automotive Applications

Automotive markets have added pressure on semiconductor/systems design through demand for ISO26262 compliance – this we all know. But they have also changed the mix of important design types. Once class of design that has become very significant in ADAS, and ultimately autonomous applications, is image signal processing (ISP).… Read More

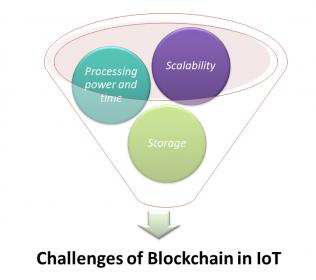

IoT and Blockchain: Challenges and Risks

The Internet of Things (IoT) is an ecosystem of ever-increasing complexity; it’s the next wave of innovation that will humanize every object in our life, and it is the next level of automation for every object we use. IoT is bringing more and more things into the digital fold every day, which will likely make IoT a multi-trillion dollar… Read More

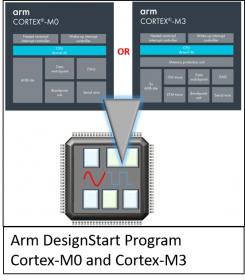

Arm and Mentor Use DesignStart Program to Accelerate Proof-of-Concept for IoT Designs

Sometimes the hardest thing about bringing a new idea to fruition is overcoming the inertia to get started with a proof-of-concept. You must be able to put together enough parts of the solution to prove to those controlling budgets that an idea has merit and is worth taking to the next level. It’s a bit of a chick-vs-egg scenario as … Read More

A Brief History of PSS at Breker

Verification engineers are hearing a lot about the Portable Stimulus Standard (PSS), and for good reason because it could potentially save them time and effort in doing their jobs much better. In order to get the big picture on what PSS is all about I contacted Adnan Hamid, founder and CEO of Breker Verification Systems, because … Read More

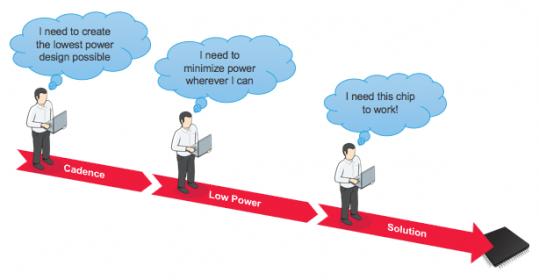

The Practice of Low Power Design

For any given design objective, there is what we in the design automation biz preach that design teams should do, and then there’s what designs teams actually do. For some domains, the gap between these two may be larger than others, but we more or less assume that methodologies which have been around for years and are considered to… Read More

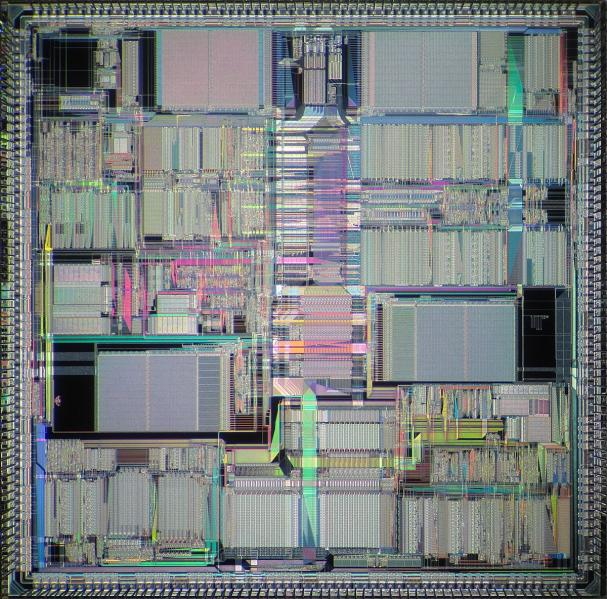

Is there anything in VLSI layout other than “pushing polygons”? (3)

In late 1986 the Layout Project Leader of DSP96000 got married and left for a 6 months’ vacation so I inherited the biggest chip MSIL had in stock. Floorplanning such size chip was a challenge from day one. Even the 68030 SUN workstation was too slow. I started to ask around and going to demos for any other possible tool that can help me… Read More

Finding the Right Needle in the IP Haystack

As the percentage of pre-configured IP increases in semiconductors, so design teams are able to reduce design cycle times. But one of the challenges for design teams is the inability to quickly and easily find IP because it’s incorrectly classified, sat in a designer’s home directory, or it’s been put into the ‘repository’ by an… Read More

Free PDF Version of PROTOTYPICAL for SoC Design

In our quest to further enlighten the masses SemiWiki has published four books, we have two more eBooks in post production due out in Q1 2018 and two more topics in research. All of the books are available free for PDF versions or you can get printed versions on Amazon.com or free printed versions at book signings or if you happen to meet… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center