The time is 1995 and my mandate as Layout Manager is to grow my team. I advertised everywhere but there were no experienced people in Canada that I can hire so the solution was back to training. I was the trainer a few times in Israel in MSIL but there we had a very organised material for layout, UNIX, software, etc. We had exercises, tests,… Read More

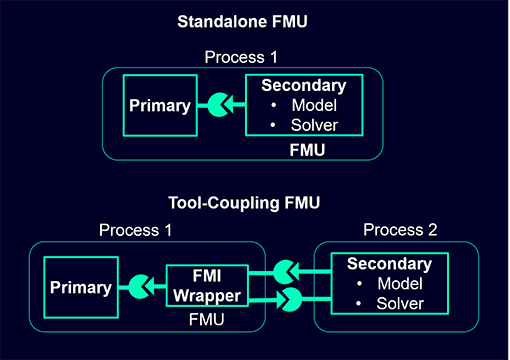

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More

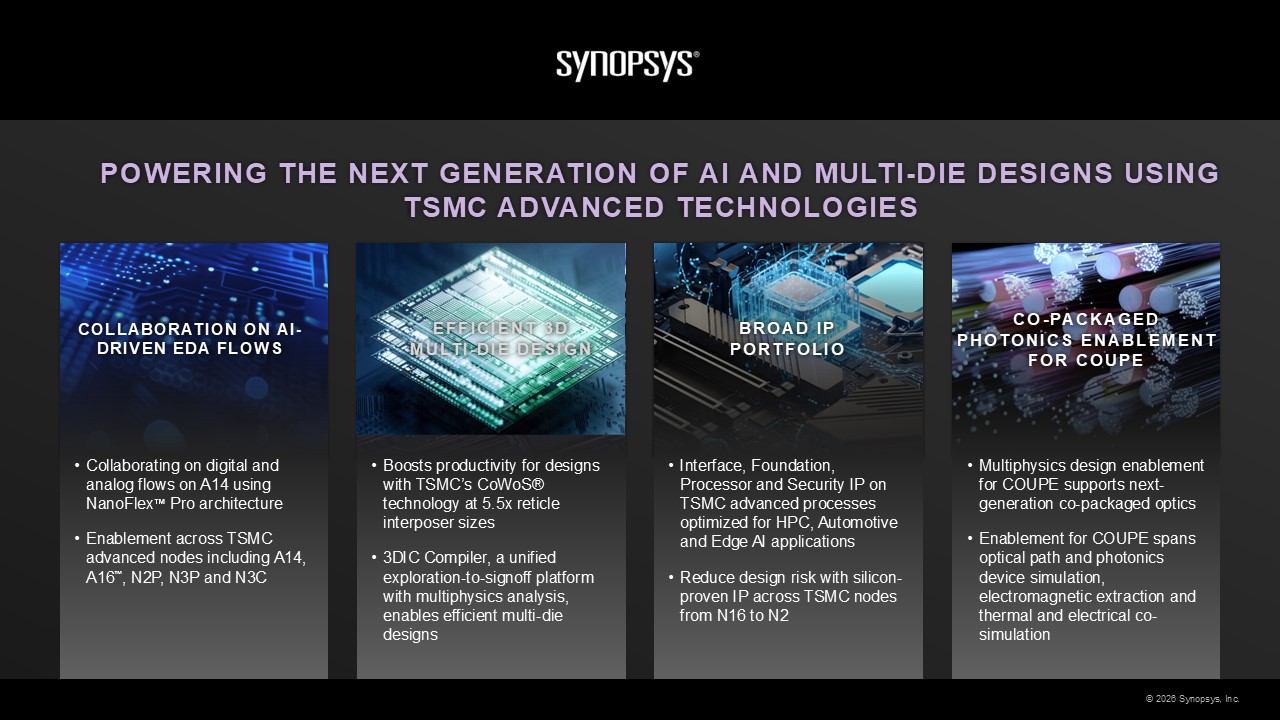

A Different Angle on Co-Simulation for SystemsCo-simulation, two or more simulations running concurrently in…Read More Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More

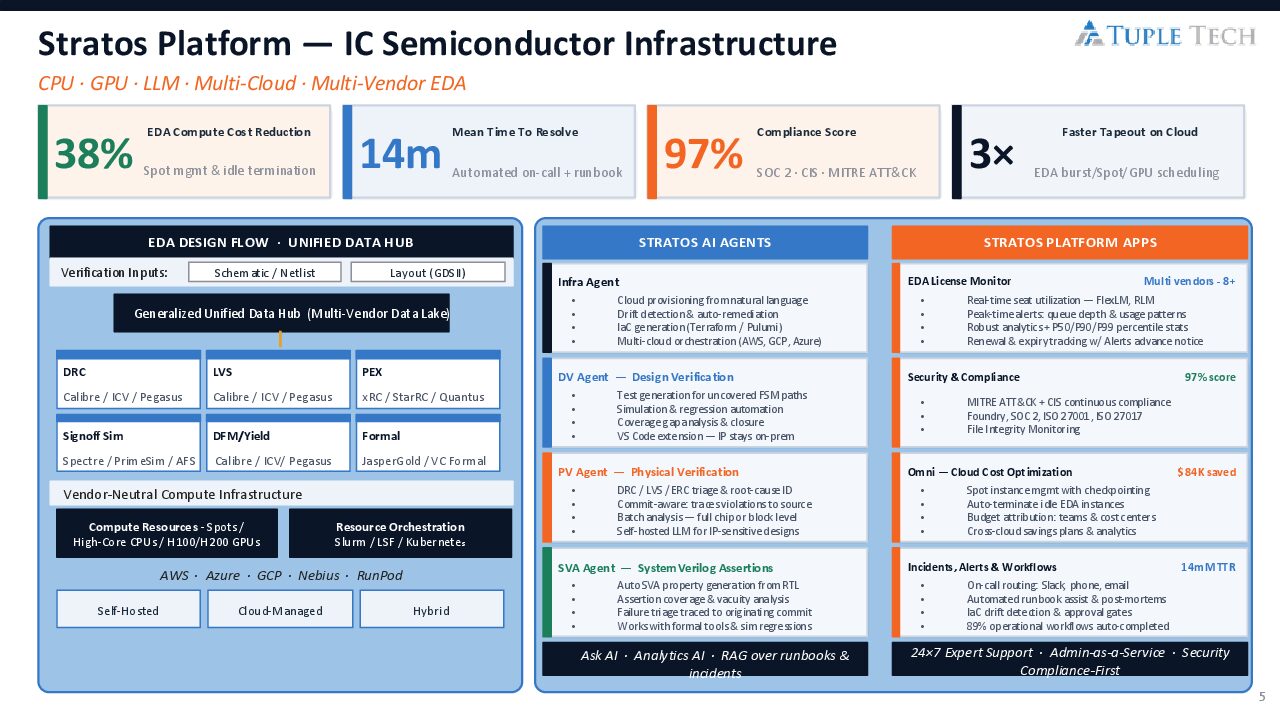

Synopsys and TSMC Deepen AI Design Alliance: What It MeansA recent announcement from Synopsys signals a meaningful…Read More Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MoreAn Advanced-User View of Applied Formal

Thanks to my growing involvement in formal (at least in writing about it), I was happy to accept an invite to this year’s Oski DVCon dinner / Formal Leadership Summit. In addition to Oski folks and Brian Bailey (an esteemed colleague at another blog site, to steal a Frank Schirrmeister line), a lively group of formal users attended… Read More

EDA and Semiconductor — Is There Growth In The Ecosystem?

The semiconductor industry has gone through several major transitions driven by different dynamics such as shift in business models (fab-centric to fab-less), product segmentation (system design house, IP developers) and end market applications (PC to cloud; and recently, to both automotive and Internet of Things — IOT’s,… Read More

Students Should Attend DAC in SFO

On LinkedIn I have some 2,116 connections and many of those are students looking to enter the field of EDA, IP or semiconductor design. What a wonderful opportunity these students have by attending the 55th annual DAC in San Francisco this summer from June 24-28. Technical sessions, keynote speeches, exhibitors, networking, … Read More

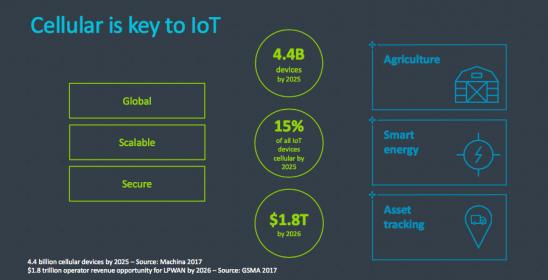

ARM and embedded SIM

It seems that a hot ticket at Mobile World Congress this year was embedded SIM announcements. As a reminder of why this space is hot, cellular communication for provisioning and data uploads is a very real option for many IoT devices. In agricultural, smart energy and asset tracking applications for example, near-range options… Read More

ClioSoft and SemiWiki Winning

There is a bit of nostalgia here since ClioSoft was one of the first companies that we (SemiWiki) worked with 7 years ago. Back then it was hard for an emerging EDA company to get noticed by the mainstream media much less collaborate with them. Since then we have published 80 blogs with ClioSoft that have garnered more than 350,000 views.… Read More

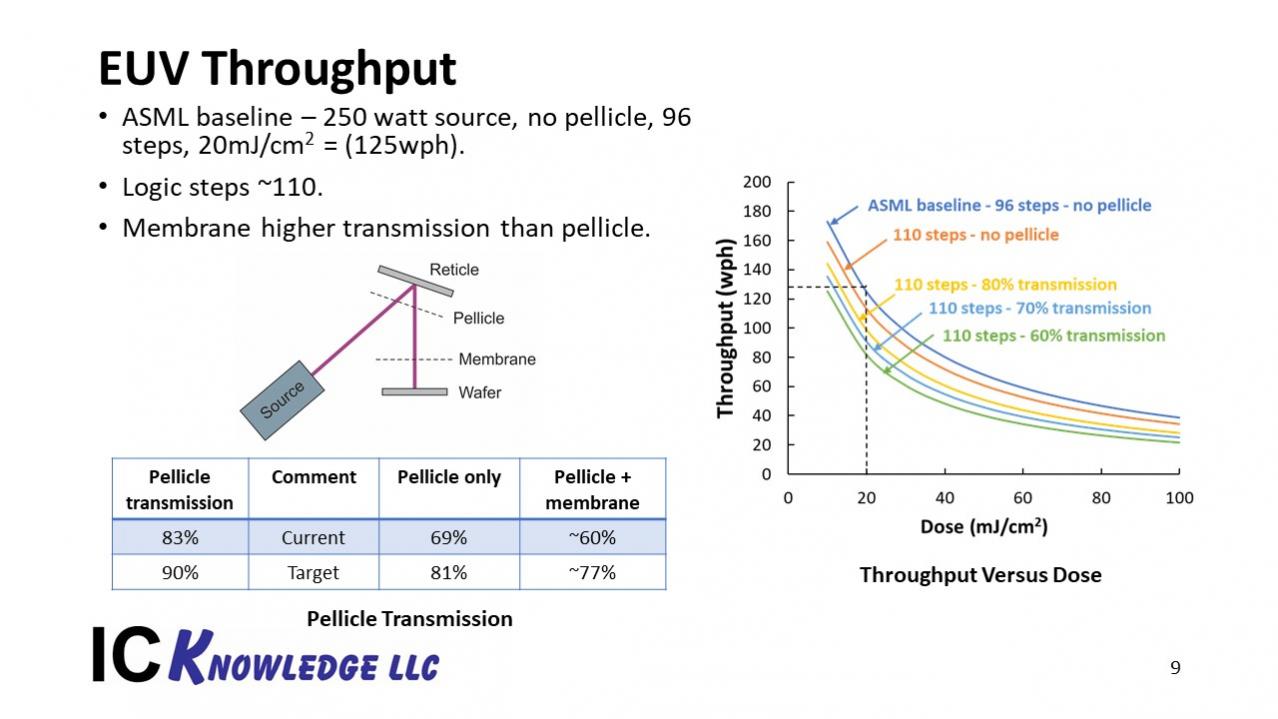

SPIE Advanced Lithography 2018 – EUV Status

This year the Advanced Lithography Conference felt very different to me than the last couple of years. I think it was Chris Mack who proclaimed it the year of Stochastics. EUV has dominated the conference for the last several years but in the past the conversation has been mostly centered on the systems, system power and uptime.

I … Read More

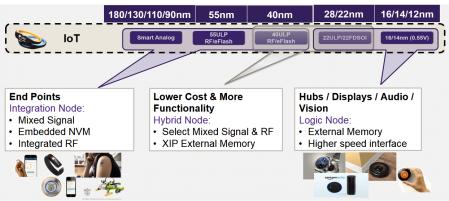

Analog-to-Digital Converter IP for IoT Designs

The projected revenue growth rate for IoT electronics remains strong, across a wide range of applications – e.g., visual object identification, voice recognition, machine automation, health and fitness applications, environmental and energy controls. A key component of these designs is the analog-to-digital conversion… Read More

MWC 2018: The Anonymous Car

European regulators are poised to once again shift European car makers to the back of the queue when it comes to realizing the value of connected cars. While the rest of the world is obsessively pursuing the creation of autonomous vehicles, the European Commission with the help of the GSMA is working toward the creation of the anonymous… Read More

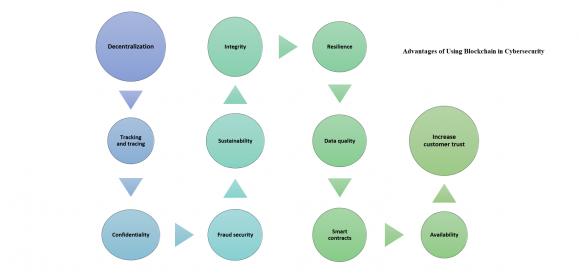

Second Line of Defense for Cybersecurity: Blockchain

In the first part we covered AI as the first line of defense for cybersecurity, the goal was to keep the cyber-criminals at bay, but in case they managed to get-in and infiltrate the network we need to initiate the second line of defense; #Blockchain. With the fact that cybercrime and cyber security attacks hardly seem to be out of the… Read More

Siemens U2U 3D IC Design and Verification Panel