You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

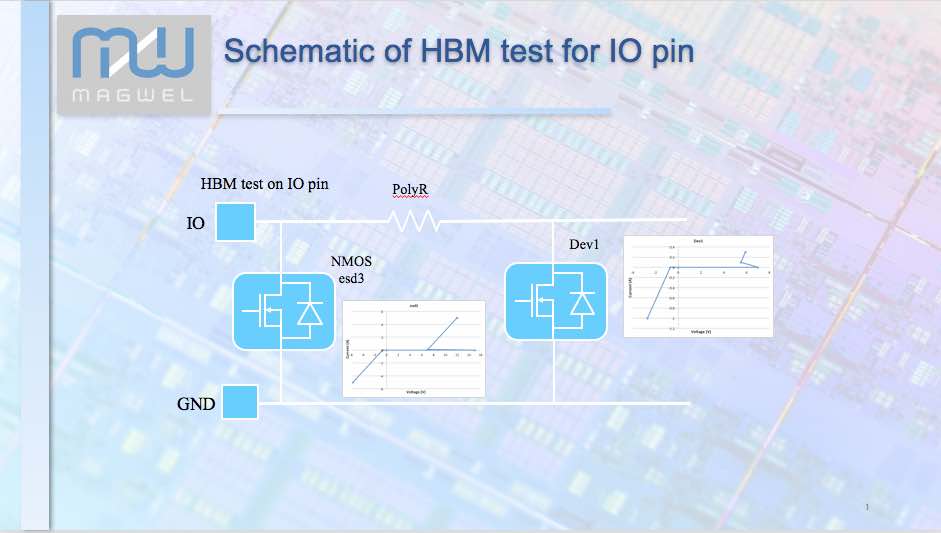

The author of this article, Dündar Dumlugöl, is CEO of Magwel. He has 25 years of experience in EDA managing the development of leading products used for circuit simulation and high-level system design.

Every designer knows how tedious it can be to shuttle back and forth between their layout tool and analysis tools. Every time an… Read More

A root of trust, particularly a hardware root of trust, has become a central principle in well-architected design for security. The idea is that higher layers in the stack, from drivers and OS up to applications and the network, must trust lower layers. What does it help it to build great security into a layer if it can be undermined… Read More

Standard cell library developers are faced with a daunting task when it is time to create a library for a new process node. Porting an existing library can be a big help, but even then, manual modifications to 800 or more cells is still required. Each of those cells has many geometric elements are that affected by new design rules. All… Read More

In the semiconductor world we have divided our engineering talent up into many adjacent disciplines and each comes with their own job titles: Design engineers, Verification engineers, DFT engineers, Test engineers. When first silicon becomes available then everyone on the team, and especially management all have a few big … Read More

Switching translates to power. Similar to the recent slow down experienced by Moore’s Law, the constant power density (power demand per unit chip area) prescribed by Dennard scaling was no longer affordable across the technological scaling. While the contribution of leakage power component in advanced process nodes was getting… Read More

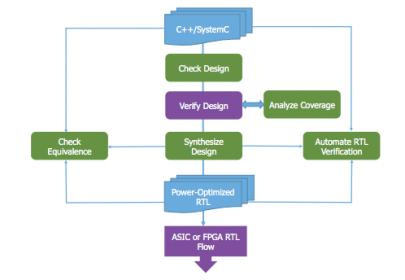

I’m on a mini-roll on the subject of high-level design for ML-based systems. No complaints from me, this is one of my favorite domains and is certainly a hot area; it’s great to that EDA vendors are so active in advancing ML-based design. Here I want to talk about the Catapult HLS flow for use in ML design.

Since I’ve covered the ML topic… Read More

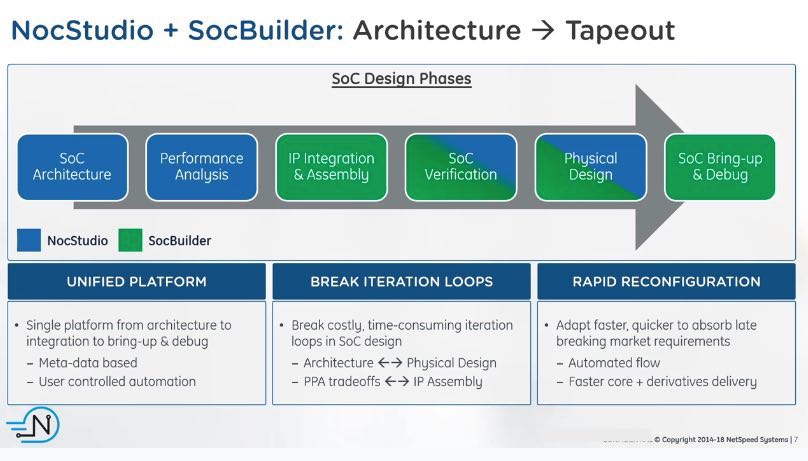

A large part of the effort in designing SOCs has shifted to the integration of their constituent IP blocks. Many IP blocks used in SOCs come as ready to use components and the real work has become making them work together. Network on Chip (NoC) has been a huge help in this task, handling the interconnections between blocks and planning… Read More

One of my favorite traditions at the Design Automation Conference is the Synopsys foundry events (the videos are now available). I learned a long time ago that the foundries are the foundation of the fabless semiconductor ecosystem and your relationships with the foundries can make or break you, absolutely. I also appreciate … Read More

Applied reported a more or less in line quarter, slightly beating weaker expectations. As we had projected, the October quarter is expected to have revenues down 10% which is at the low end of our expected 10-15% drop in business. Applied services helped partially make up for some of the equipment sales weakness. Revenue came in … Read More

Applied Materials (AMAT) is batting clean up in a quarter that has not been pretty. Lately semi stocks seem to have been hit by not only stock specific issues but continued and increasing memory concerns coupled with more macro issues. On top of all this, China trade issues which have in the meantime taken a back burner to other issues… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center