The automotive industry continues push the limits on how “smart” we can make our vehicles and from that, it follows as to how smart we can make the electronics in the vehicles. When I think of smart cars (and smart automotive ICs) I typically think of things like advanced driver-assistance systems (ADAS) that use AI and neural networks for image recognition and automated driving controls. However, there is another level intelligence going on inside the ICs that is just as critical but maybe not so well known.

The automotive industry continues push the limits on how “smart” we can make our vehicles and from that, it follows as to how smart we can make the electronics in the vehicles. When I think of smart cars (and smart automotive ICs) I typically think of things like advanced driver-assistance systems (ADAS) that use AI and neural networks for image recognition and automated driving controls. However, there is another level intelligence going on inside the ICs that is just as critical but maybe not so well known.

What I’m alluding to is the use of design-for-test (DFT) technologies in ICs that do self-monitoring, error detection and self-correction. While perhaps not as glamorous as AI or neural networks, these capabilities are essential technology to all ICs in safety-critical applications. Traditionally, DFT techniques have been used to improve the cost and coverage of post-manufacturing tests meant to ensure that chips don’t ship to customers with internal manufacturing defects. More recently however, DFT has grown to encompass a larger scope known as mission-mode testing.

Mission-mode testing entails self-diagnostic testing by chips during power-on, power-off and certain runtime scenarios. These tests are meant to check for errors that may have creep in over time while the chip is being used (e.g. errors caused by aging or environmental considerations or some unexpected or unplanned state, either accidental or nefarious). In-system test (IST) challenges are much like those seen at manufacturing test where we are dealing with large complex circuits with deeply embedded logic that can be hard to access and isolate. Additionally, IST also has the requirement of being able to run these tests in real time while accommodating required system response times and power budgets.

Mentor, a Siemens Business, has been working on this issue for their automotive customers and has recently added a new technology called Tessent MissionMode to their test-products portfolio. Tessent MissionMode has both design tool and IP components. The design tool portion is the Tessent Shell tool that enables designers to insert a MissionMode IST controller-IP into their chip designs. The controller block is a central control hub that connects and manages test blocks spread throughout the chip such as built-in-self-test (BIST) circuitry for memories (MBIST), logic (LBIST) and other on-chip test industry-interface compliant structures. These test blocks monitor and check the chip’s functions, returning status to the controller on an ongoing basis. If trouble is spotted the controller sends a signal to the chip’s main CPU for action.

Mentor, a Siemens Business, has been working on this issue for their automotive customers and has recently added a new technology called Tessent MissionMode to their test-products portfolio. Tessent MissionMode has both design tool and IP components. The design tool portion is the Tessent Shell tool that enables designers to insert a MissionMode IST controller-IP into their chip designs. The controller block is a central control hub that connects and manages test blocks spread throughout the chip such as built-in-self-test (BIST) circuitry for memories (MBIST), logic (LBIST) and other on-chip test industry-interface compliant structures. These test blocks monitor and check the chip’s functions, returning status to the controller on an ongoing basis. If trouble is spotted the controller sends a signal to the chip’s main CPU for action.

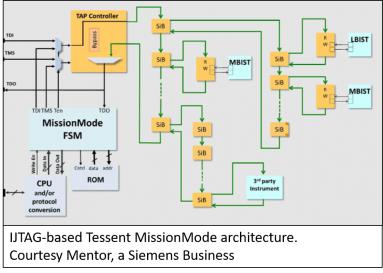

Because systems-on-chip (SoCs) are so complex, Mentor has taken a hierarchical approach to their testing architecture that lets engineers break their designs into hierarchical zones within the chip that can be alternately enabled or disabled using segment-insertion bit (SIB) IP switch blocks. Each test block can be a different type of test. Test blocks can also be hierarchical themselves. The MissionMode controller communicates with different test blocks using the industry standard IJTAG protocol, telling each test block what tests to perform and when to perform them. Negative results can be communicated back to the main CPU which can then take the appropriate action to record, report or fix the problem. The hierarchical nature of the test network allows designers to ensure low latency between the test controller and various test blocks, which is important as time budgets for in-system tests are typically small.

Because systems-on-chip (SoCs) are so complex, Mentor has taken a hierarchical approach to their testing architecture that lets engineers break their designs into hierarchical zones within the chip that can be alternately enabled or disabled using segment-insertion bit (SIB) IP switch blocks. Each test block can be a different type of test. Test blocks can also be hierarchical themselves. The MissionMode controller communicates with different test blocks using the industry standard IJTAG protocol, telling each test block what tests to perform and when to perform them. Negative results can be communicated back to the main CPU which can then take the appropriate action to record, report or fix the problem. The hierarchical nature of the test network allows designers to ensure low latency between the test controller and various test blocks, which is important as time budgets for in-system tests are typically small.

This self-diagnostic and self-correction or mitigation functionality has many applications. Errors can be reported to an automobile’s main controller, which in turn can warn drivers of a problem in real-time and even take corrective action to self-repair the problem or return to a safe state. Additionally, data can be sent to service centers and manufacturers for follow-up action, root-cause analysis and design corrections to be captured in future versions of the chip. Finding the source of defects and fixing them is imperative for the automotive industry as it strives to achieve zero-defect ICs for autonomous vehicles.

The Tessent MissionMode IP and other Mentor DFT blocks provide users with an ISO 26262 qualification report to simplify chip ASIL certification and have been tuned to work with the rest of Mentor’s DFT design tool solutions. In case you are wondering if this is all just hype, or if anyone is using this technology, you have no further to look than to a recent announcement by Mentor and Renesas where Renesas touted their use of Mentor Tessent products to reduce their costs and improve the quality of their automotive-IC manufacturing and in-systems tests (see link below).

So, not only are automobiles becoming smart enough to detect objects and avoid them, but the ICs inside those vehicles are also becoming smart enough to intelligently monitor themselves and act should things take a turn for the worse. Remembering the adage, a chain is only as strong as its weakest link, Mentor’s Tessent MissionMode offering is all about ensuring that the ICs in your automobiles won’t be that weak link.

See also:

Renesas use of Mentor’ Tessent Products for Automotive ICs

Mentor Tessent Mission Mode white paper

Mentor Tessent Products

Comments

There are no comments yet.

You must register or log in to view/post comments.