Digital logic chips synchronize all logic operations by using a clock signal connected to flip-flops or latches, and the clock is distributed across the entire chip. The ultimate goal is to have a clock signal that arrives at the exact same moment in time at all clocked elements. If the clock arrives too early or too late from the PLL… Read More

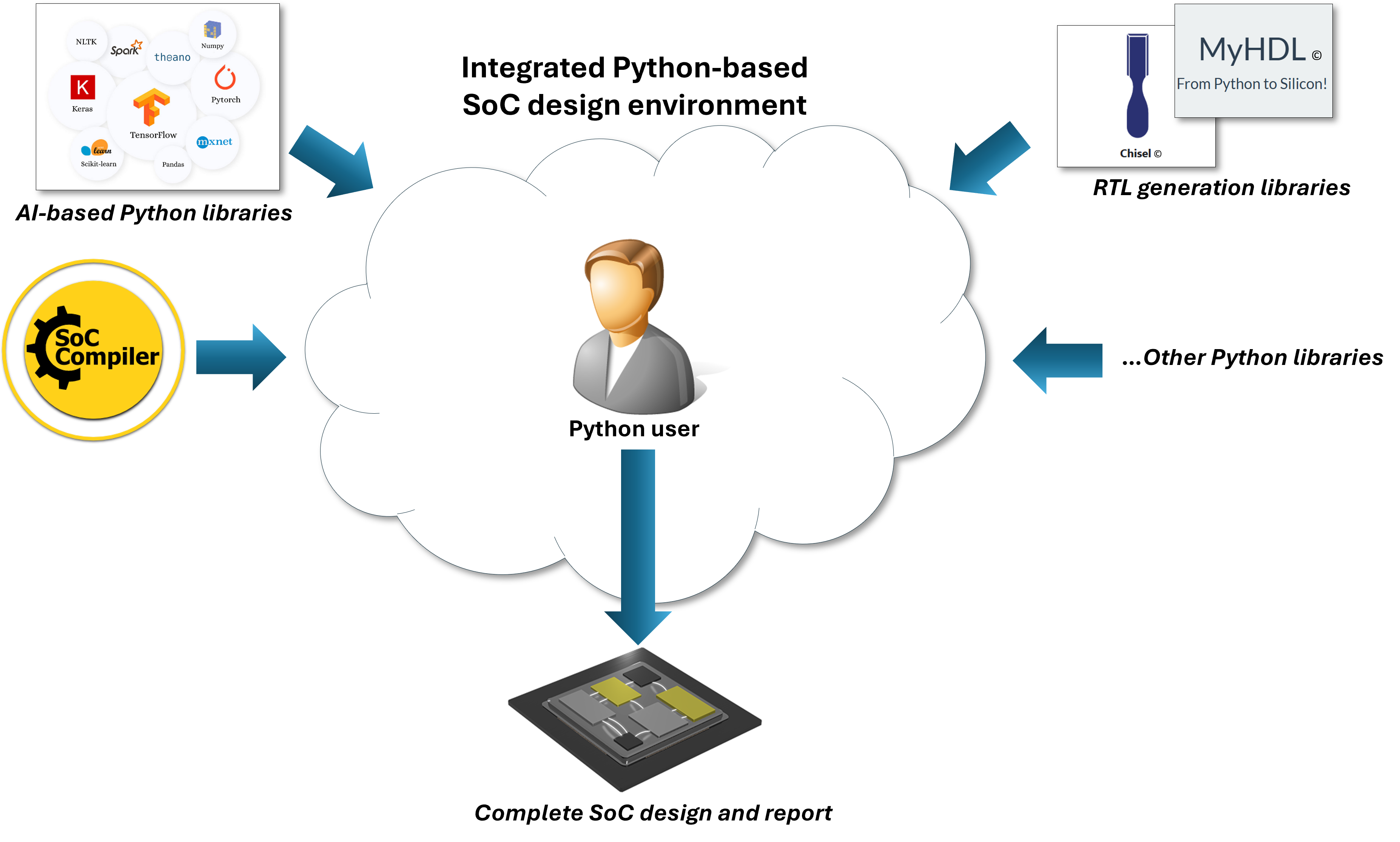

Build a 100% Python-based Design environment for Large SoC DesignsIn the fast-evolving world of semiconductor design, chip…Read More

Build a 100% Python-based Design environment for Large SoC DesignsIn the fast-evolving world of semiconductor design, chip…Read More Keysight EDA 2025 launches AI-enhanced design workflowsThe upcoming Keysight EDA 2025 launch has three…Read More

Keysight EDA 2025 launches AI-enhanced design workflowsThe upcoming Keysight EDA 2025 launch has three…Read More Changing RISC-V Verification Requirements, Standardization, InfrastructureA lively panel discussion about RISC-V and open-source…Read More

Changing RISC-V Verification Requirements, Standardization, InfrastructureA lively panel discussion about RISC-V and open-source…Read More Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V SolutionFounded with a vision to create transformative, customizable…Read More

Semidynamics: A Single-Software-Stack, Configurable and Customizable RISC-V SolutionFounded with a vision to create transformative, customizable…Read More Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early AdoptersThe demand for high-performance computing (HPC), data centers,…Read More

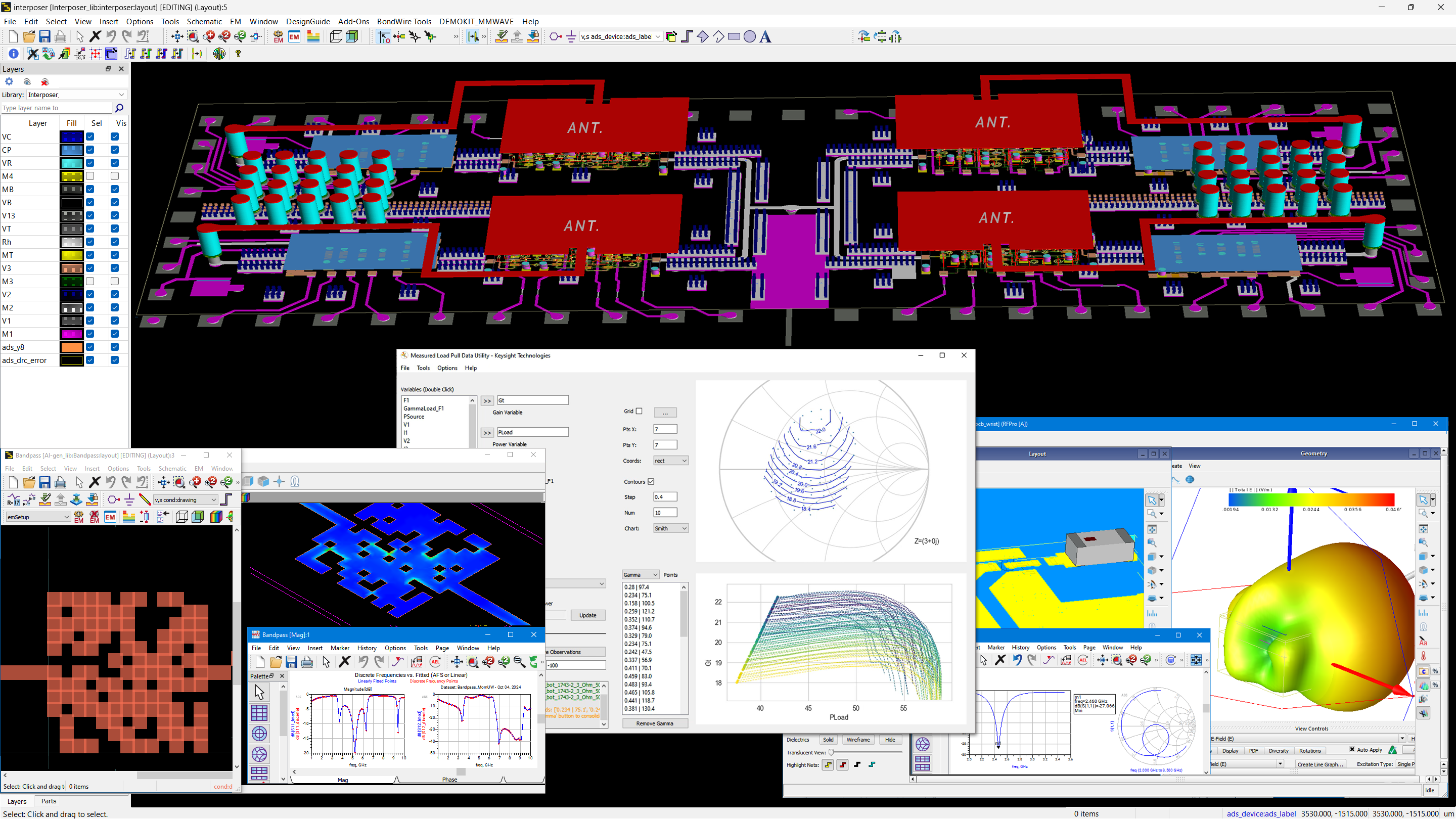

Synopsys-Ansys 2.5D/3D Multi-Die Design Update: Learning from the Early AdoptersThe demand for high-performance computing (HPC), data centers,…Read MoreCan Correlation Between Simulation and Measurement be Achieved for Advanced Designs?

“What you simulate is what you get.” This is the holy grail of many forms of system design. Achieving a high level of accuracy between predicted and actual performance can cut design time way down, resulting in better cost margins, time to market and overall success rates. Achieving a high degree of confidence in predicted performance… Read More

Measuring Local EUV Resist Blur with Machine Learning

Resist blur remains a topic that is relatively unexplored in lithography. Blur has the effect of reducing the difference between the maximum and minimum doses in the local region containing the feature. Blur is particularly important for EUV lithography since EUV lithography is prone to stochastic fluctuations and also driven… Read More

Podcast EP212: A View of the RISC-V Landscape with Synopsys’ Matt Gutierrez

Dan is joined by Matt Gutierrez. Matt joined Synopsys in 2000 and is currently Sr. Director of Marketing for Processor & Security IP and Tools. His current responsibilities include the worldwide marketing of ARC Processors and Subsystems, Security IP, and tools for the development of application-specific instruction … Read More

CEO Interview: Patrick T. Bowen of Neurophos

Patrick is an entrepreneur with a background in physics and metamaterials. Patrick sets the vision for the future of the Neurophos architecture and directs his team in research and development, particularly in metamaterials design. He has a Master’s degree in Micro-Nano systems from ETH Zurich and PhD in Electrical Engineering… Read More

Checking and Fixing Antenna Effects in IC Layouts

IC layouts go through extensive design rule checking to ensure correctness, before being accepted for fabrication at a foundry or IDM. There’s something called the antenna effect that happens during chip manufacturing where plasma-induced damage (PID) can lower the reliability of MOSFET devices. Layout designers run Design… Read More

Arteris is Unleashing Innovation by Breaking Down the Memory Wall

There is a lot of discussion about removing barriers to innovation these days. Semiconductor systems are at the heart of unlocking many forms of technical innovation, if only we could address issues such as the slowing of Moore’s Law, reduction of power consumption, enhancement of security and reliability and so on. But there … Read More

2024 Outlook with Elad Alon of Blue Cheetah Analog Design

We have been working with Blue Cheetah Analog Design for three years now with great success. With new process nodes coming faster than ever before and with chiplets being pushed to the forefront of technology, the die-to-die interconnect traffic on SemiWiki has never been greater and chiplets is one of our top search terms.

Tell… Read More

Automotive Electronics Trends are Shaping System Design Constraints

Something is brewing in automotive electronics. Within a one-month window most of the product announcements and pitches to which I am being invited are on automotive topics. Automotive markets have long been one of the primary targets for suppliers to system designers, but this level of alignment in announcements seems more … Read More

2024 Outlook with Jim Cantele of Altair

Jim Cantele, global SVP of sales and technology at Altair, is an electronics industry veteran with deep knowledge of EDA software and services. Before joining Altair during the acquisition of Runtime Design Automation in 2017, Jim held executive-level management positions at a number of leading EDA and semiconductor companies,… Read More

Build a 100% Python-based Design environment for Large SoC Designs