Probably the most interesting news out of 56thDAC thus far is the announcement that in 2020 and 2021 DAC will co-locate with SEMICON West. It’s great news really since this is something that has been discussed over the years but has been deadlocked due to “failed negotiations”. Unfortunately, simple logic goes out the window with… Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

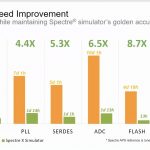

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreParallel SPICE Circuit Simulator Debuts

In EDA the most successful companies will often re-write their software tools in order to add new features, improve accuracy, increase capacity and of course, shorten run times. For SPICE circuit simulators we typically look at several factors to see if a new tool is worth a look or not:

- Netlist compatibility

- Model support

- Foundry

A Practical Approach to Modeling ESD Protection Devices for Circuit Simulation

Lurking inside of every Mosfet is a parasitic bipolar junction transistor (BJT). Of course, in normal circuit operation the BJT does not play a role in the device operation. Accordingly, SPICE models for Mosfets do not behave well when the BJT is triggered. However, these models work just fine for most purposes. The one important… Read More

The Genius Sperm Bank

The “20 Questions with John East” series continues

How did it happen? How did Fairchild transform over a decade into the “off with their heads” culture? To understand that, you need to know a little about the William Shockley story. William Shockley was born in London in 1910. He moved to Silicon Valley when he was 3. Of course,… Read More

Needham is Upbeat about EDA and IP Growth at #56DAC

It’s Sunday afternoon and I just attended the annual Needham presentation at #56DAC in sunny Las Vegas, where Rich Valera shared an upbeat view of EDA and IP growth. Here are the five drivers of this growth:

- IoT

- Automotive

- Webscale/FAANGs

- AI/ML

- China

For the IoT market they’ve seen a CAGR of 8.6% to $8.2B in 2018, projected… Read More

In Their Own Words: TSMC and Open Innovation Platform

TSMC, the largest and most influential pure-play foundry, has many fascinating stories to tell. In this section, TSMC covers some of their basic history, and explains how creating an ecosystem of partners has been key to their success, and to the growth of the semiconductor industry.

The history of TSMC and its Open Innovation … Read More

In Their Own Words: eSilicon Corporation

eSilicon was one of the first companies to focus on making the benefits of the fabless semiconductor movement available to a broader range of customers and markets. The company is credited with the creation of the fabless ASIC model. In this section, eSilicon shares some of its history and provides its view of the ever-changing … Read More

Ten Things to see @ 56th DAC!

New products always take precedence since EDA is a “mature” market. I have inside knowledge on this one so I can tell you it is not to be missed. Coincidently, but not really, a related white paper was just published so if you are not going to 56thDAC you can still get a virtual briefing. If you are going to DAC be sure and stop by the Fractal… Read More

Will a Lack of Ethics Doom Artificial Intelligence

If there was ever a time that ethics should be formally applied to technology, it is with the emergence of Artificial Intelligence. Yet most of the big AI companies struggle with what should seem a simple task: defining ethics for the use of their products. Without the underpinnings of a moral backbone, powerful tools often become… Read More

Siemens Shows SOC Simulation Solution for Self-Driving Vehicles

Ever since the early days of computing there has always been a large distinction between ‘regular’ computing and real time computing – where special care had to be made to deal with unordered and asynchronous events. Back then a system typically consisted of a handful of sensors and perhaps some electromechanical devices.… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center